### lecture 3- Layout I omg I

We have circuit in schematic? Now we want to put that circuit on a board while considering parasitics, manufacturing, and signal integrity?

## **Follow these** guys on instagram @mit\_solar\_car

## **ANNOUNCEMENT - END OF IAP DANCY PARTY!!!**

(This class is about Art + Science, so we can't justttt do something intellectual to celebrate the fact that you can design PCBS! We need to include art!)

(So we're having a dance party - w/ food ofc)

## Wed, Feb 1st, 7-9 PM! @ Lobby 13

(Yes, you can invite your friends!)

## OUTLINE

- what is layout / Electron herding / steps to layout

- Placing components - Tools for connection

- Layout considerations

- CASE STUDIES ON GOOD LAYOUT!!!

### (Introduction to urban planning for the distinguished electrical engineer)

## Layout is the FUN PART!

## (This is where the ART comes in, a good layout is like a beautiful little metropolis of electrons)

(You herd these electrons where they need to go using layout)

### Get ready.

### **^ you're responsible for the** child in the middle

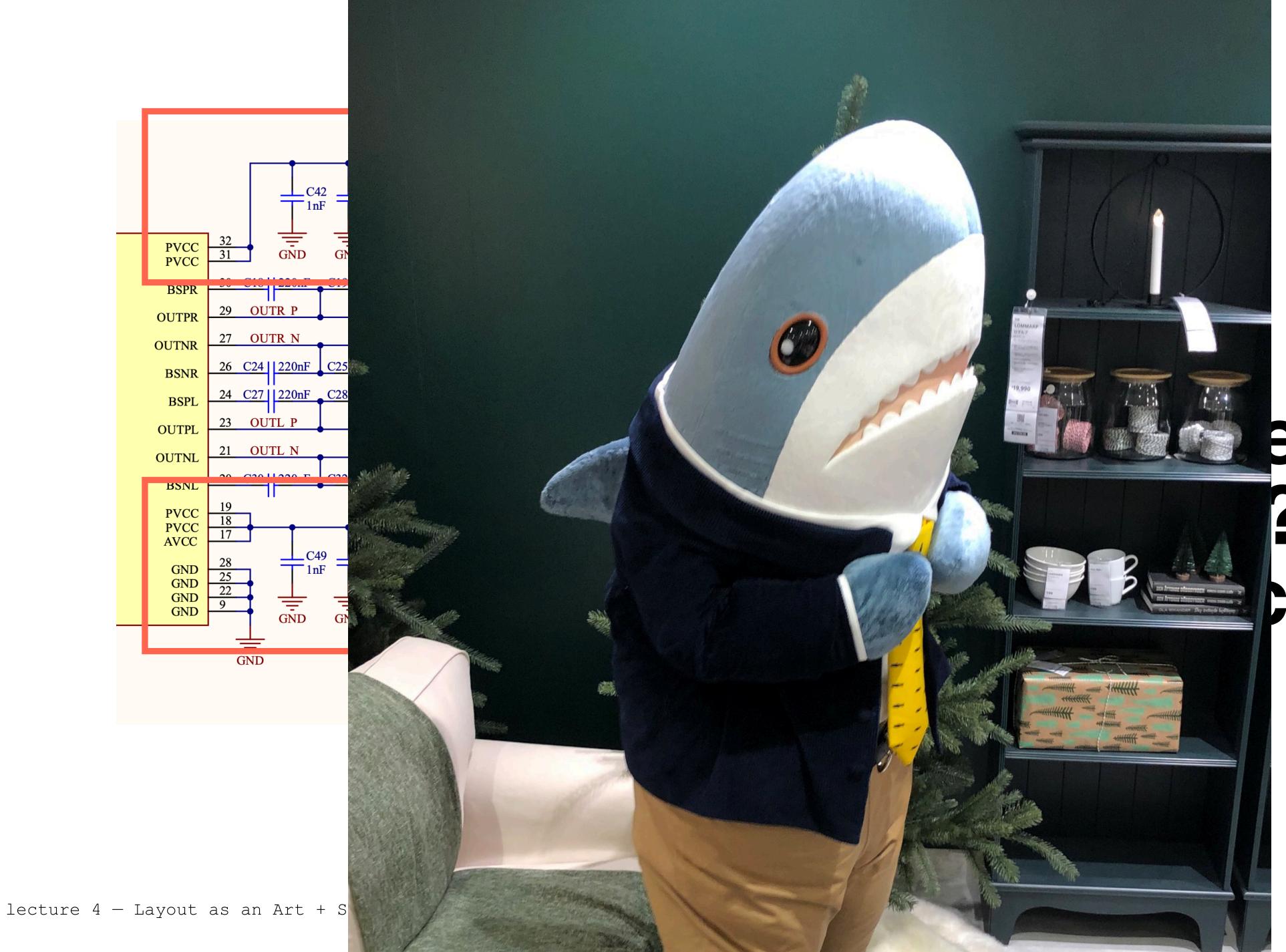

lecture 4 - Layout as an Art + Science | pcb.mit.edu | yaypcbs@mit.edu

# electron neutron

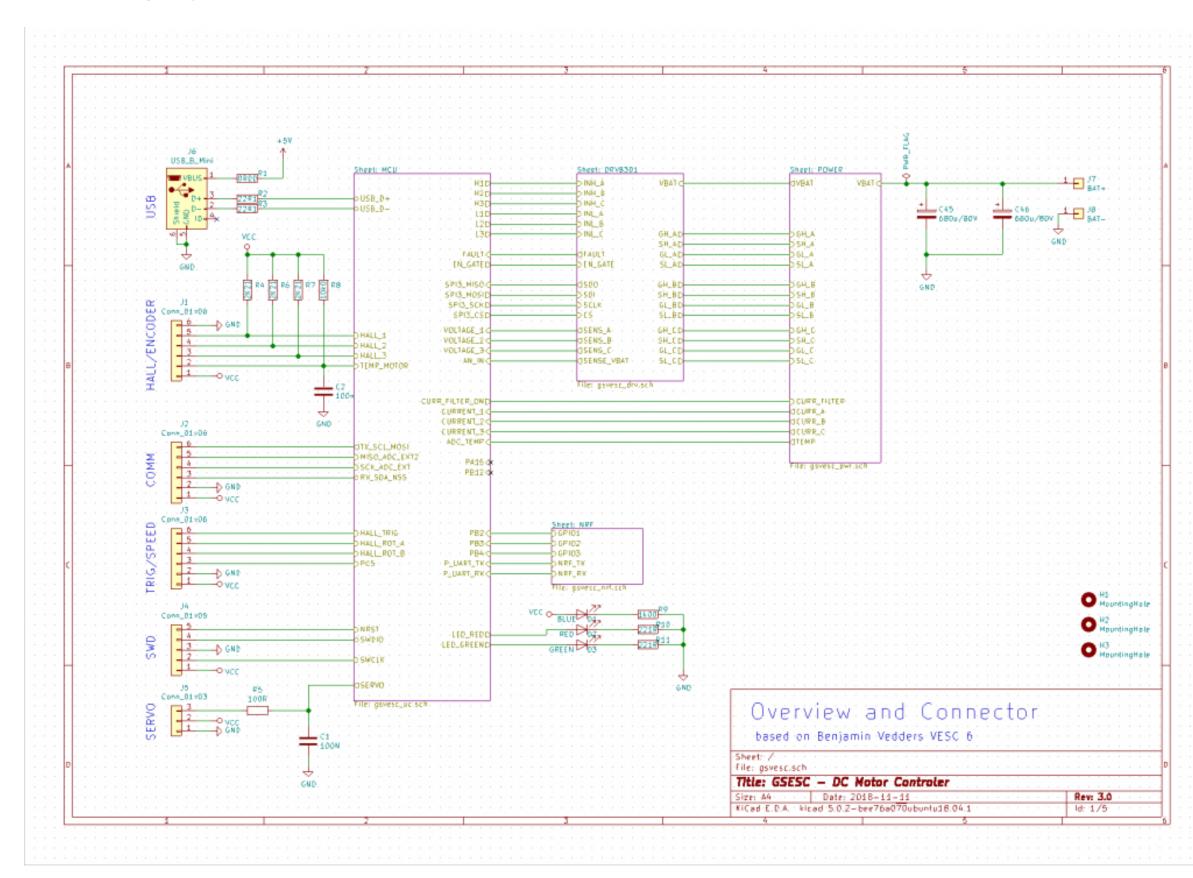

### vesc-project.com

### (This is where we connect everything yes, but it's also where we consider all the un-ideal things that happen in the real world and how we can fix them with design)

lecture 4 - Layout as an Art + Science | pcb.mit.edu | yaypcbs@mit.edu

PCRDESIGN

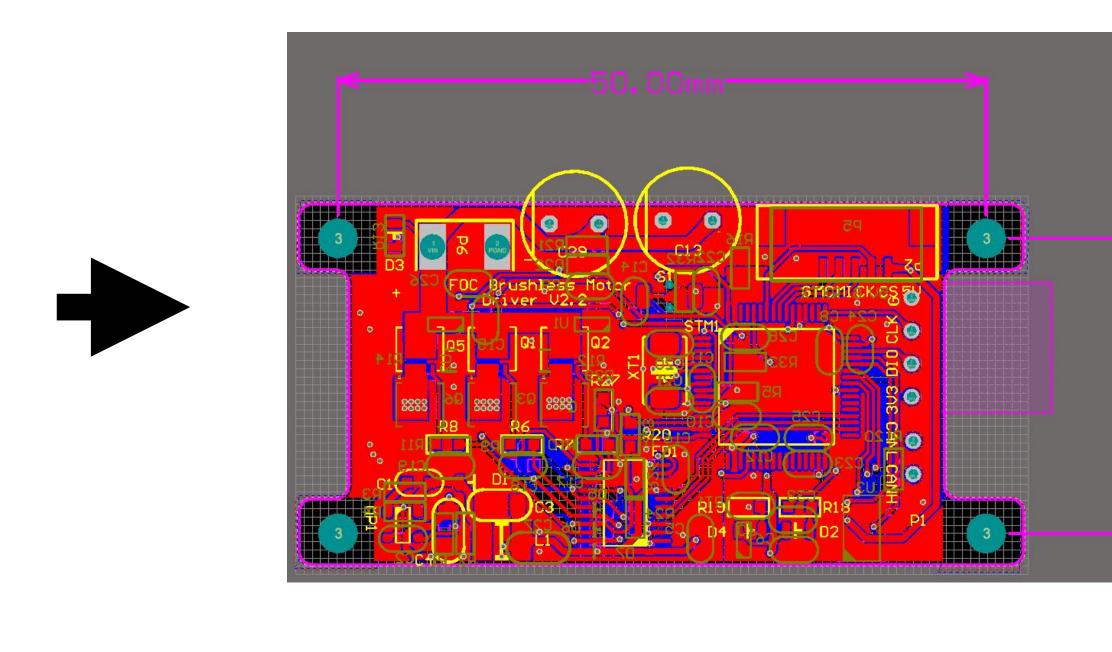

### **Components on the board,** placement & orientation!

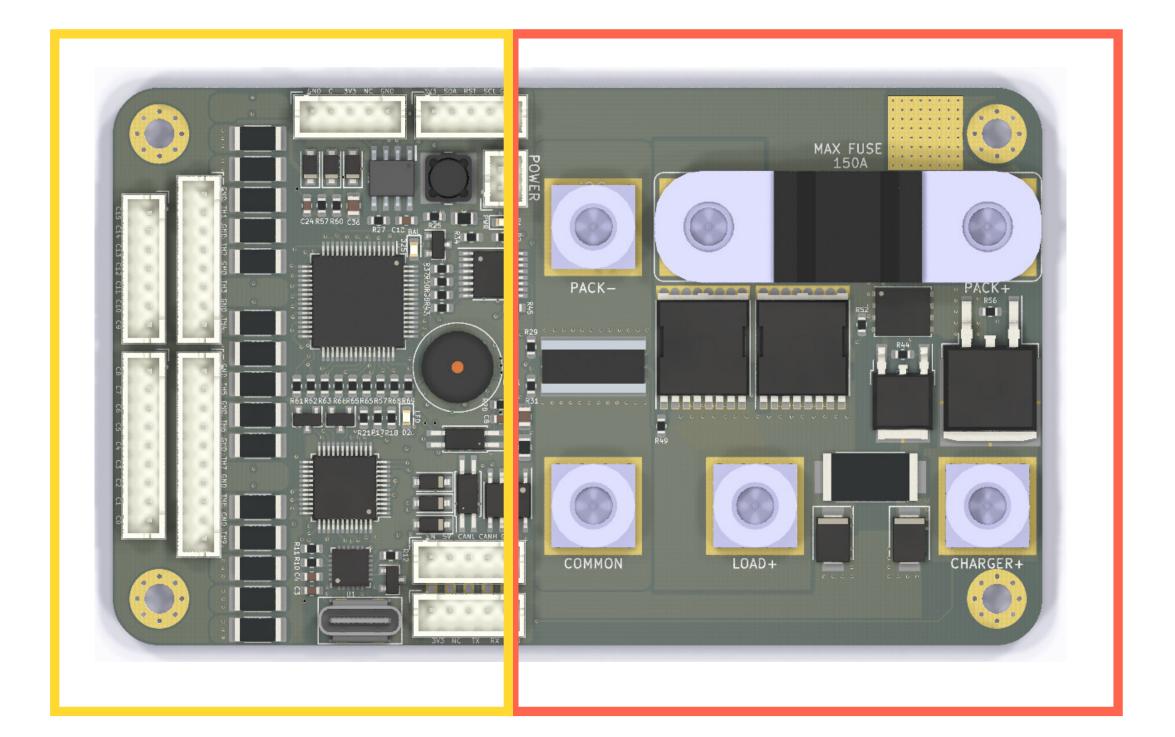

### Separation of Power + Signal.

lecture 4 - Layout as an Art + Science | pcb.mit.edu | yaypcbs@mit.edu

https:// www.dreamstime.com/ illustration/isometriccity-blocksconcept.html

# **Signal block**

# Tell me whyyy?? (Ain't nothing but a partttyyyyy...)

lecture 4 - Layout as an Art + Science | pcb.mit.edu | yaypcbs@mit.edu

SCIE SCIE DCB

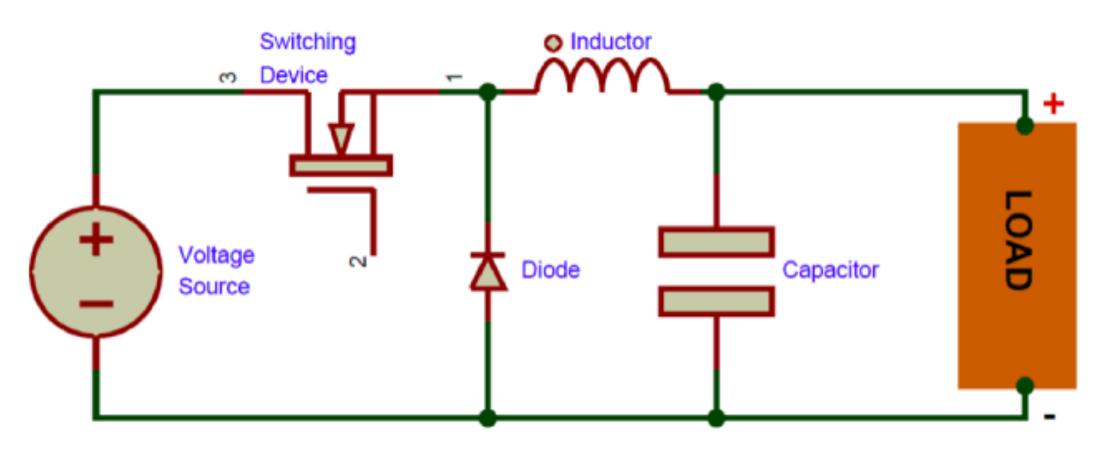

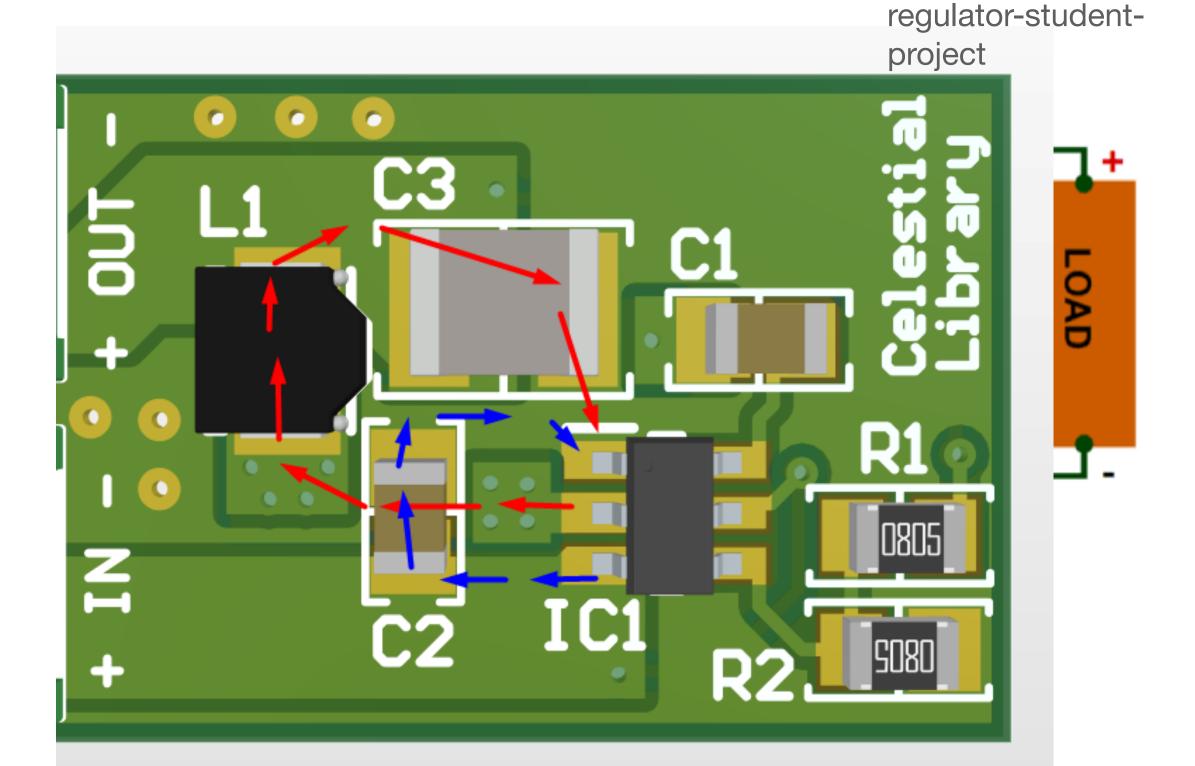

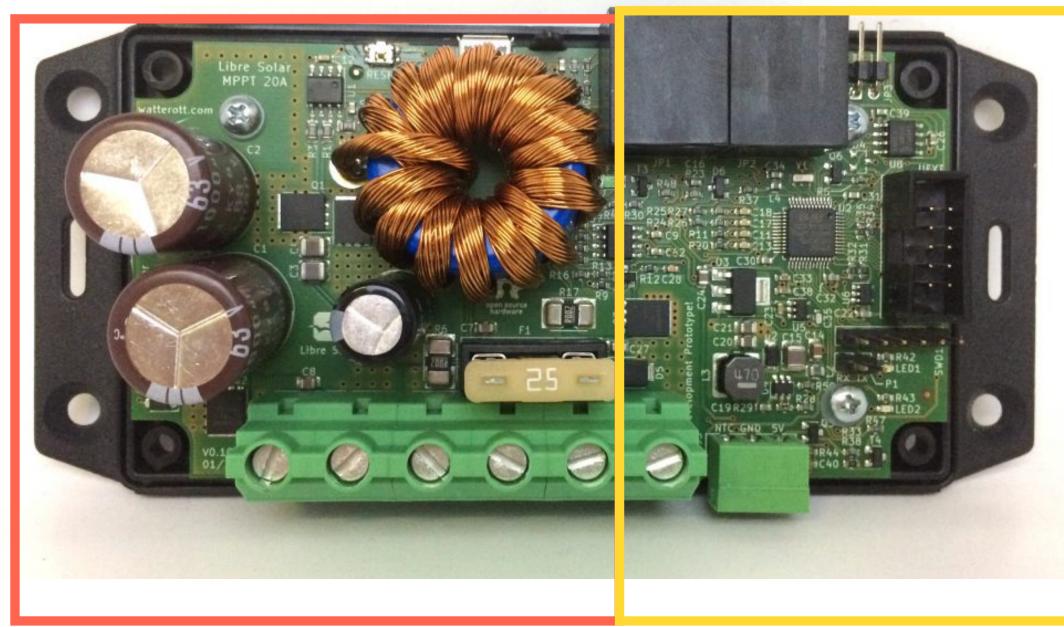

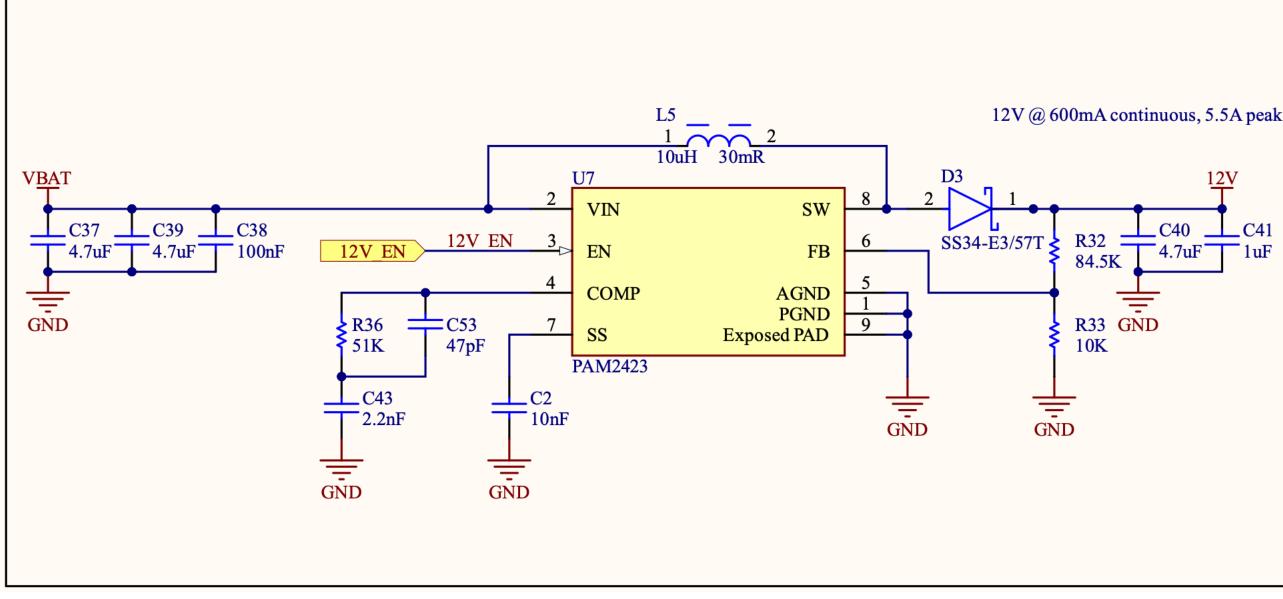

### Power, LDOs, Switching Converters, Digital, Analog

https://components101.com/articles/buckconverter-basics-working-design-and-operation

### (Put these far from sensitive electronics, switching produces noise!)

lecture 4 - Layout as an Art + Science | pcb.mit.edu | yaypcbs@mit.edu

SCIED PCRDESIGN

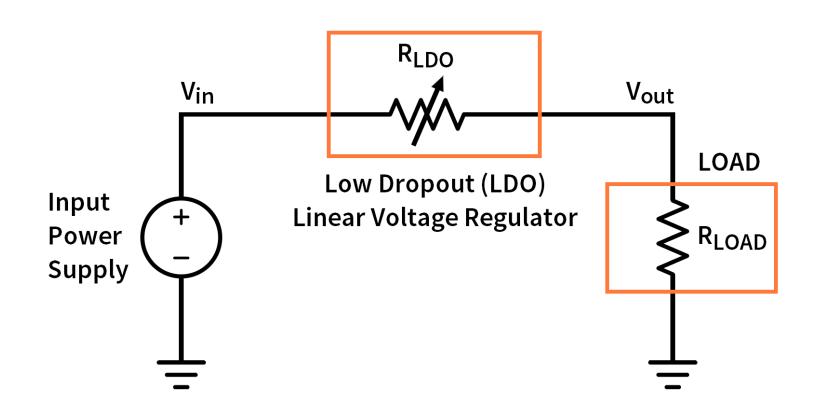

https://www.circuitbread.com/ee-faq/when-shouldyou-choose-ldo-or-buck-converter

### (Put these NEAR chips, because they SMOOTH the voltage signal, small trace so less time to pick up noise)

### Power, LDOs, Switching Converters, Digital, Analog https:// resources.altium.com/p/ build-dc-dc-buck-

### (As tightly packaged as possible)

lecture 4 - Layout as an Art + Science | pcb.mit.edu | yaypcbs@mit.edu

PCBDESIGN

https://sg.rs-online.com/web/p/ voltage-regulators/9210603

### (Put these NEAR chips, because they SMOOTH the voltage signal, small trace so less time to pick up noise)

## Separation of Power + Signal.

Signal

https://forum.esk8.news/t/ diebiems-fork-ennoid-bmsfor-6s-to-24s-battery-packs/ 45490?page=6

Power

lecture 4 - Layout as an Art + Science | pcb.mit.edu | yaypcbs@mit.edu

## SCIENCE DESIGN

### https://www.fablab-hamburg.org/the-libre-solar-project/

### Power

### Signal

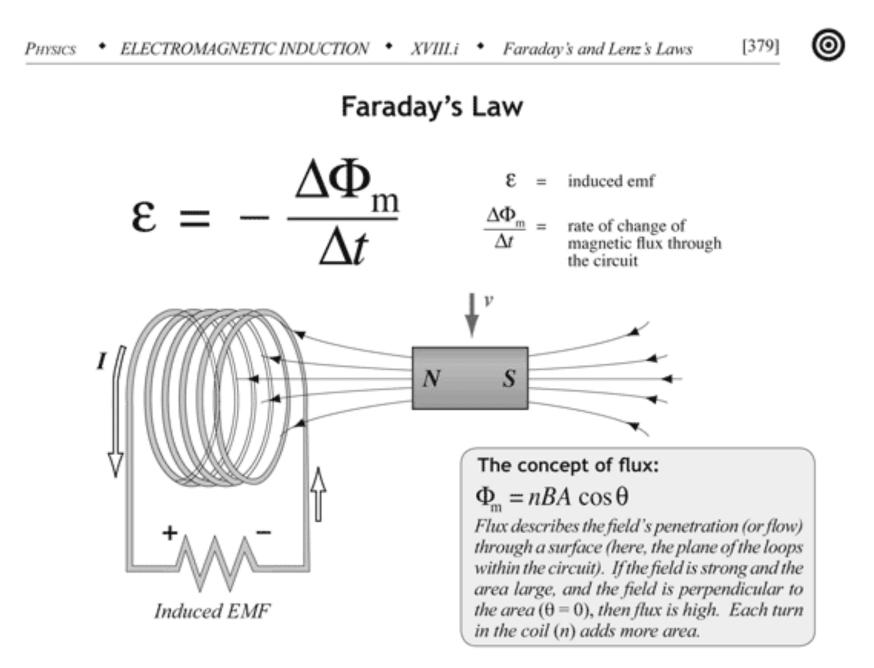

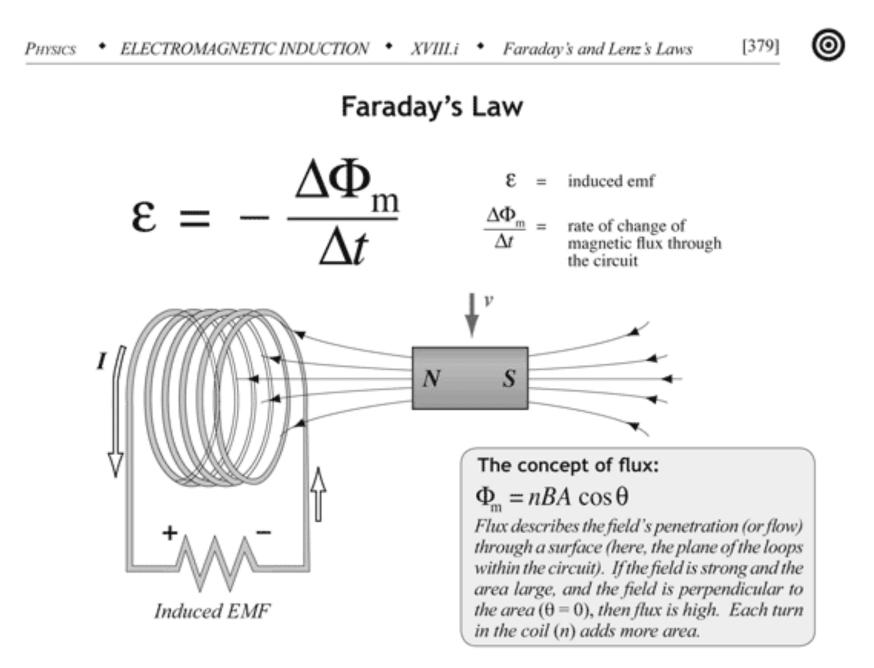

### **Orientation + Minimization** of Trace Length, Inductance Loops.

https://sites.suffolk.edu/kdshepard/2013/03/07/faradays-law/

lecture 4 - Layout as an Art + Science | pcb.mit.edu | yaypcbs@mit.edu

## PCRDESIGN

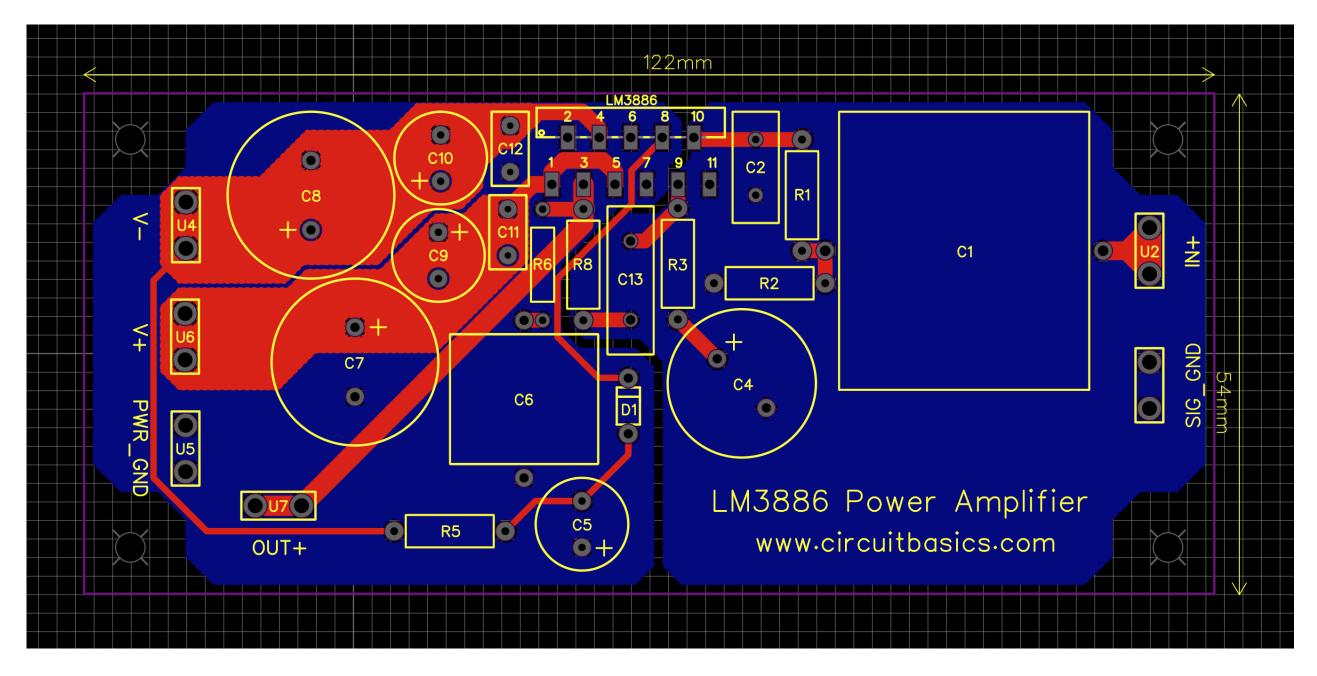

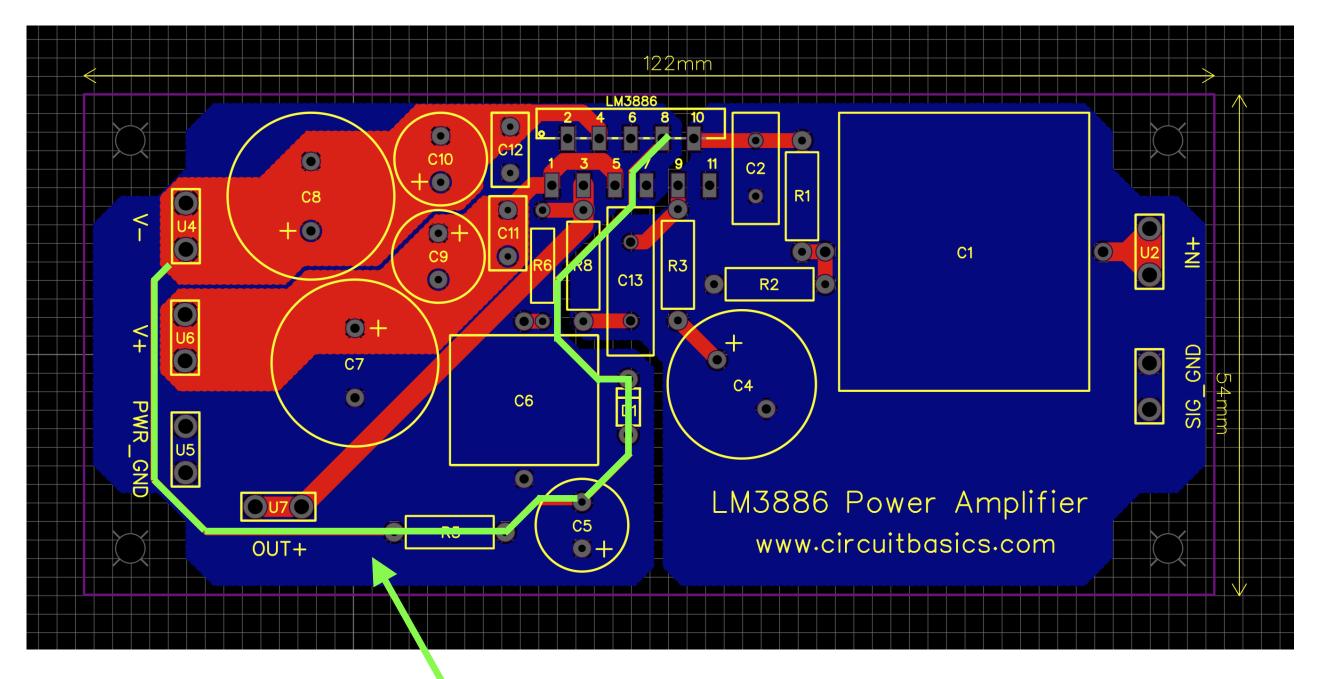

https://www.circuitbasics.com/what-is-pcb-design/

### **Orientation + Minimization** of Trace Length, Inductance Loops.

https://sites.suffolk.edu/kdshepard/2013/03/07/faradays-law/

lecture 4 - Layout as an Art + Science | pcb.mit.edu | yaypcbs@mit.edu

## PCRDESIGN

https://www.circuitbasics.com/what-is-pcb-design/

### Very Large Loop = Bad, especially near power components

### **Tightly Packing** Components (similar idea).

lecture 4 - Layout as an Art + Science | pcb.mit.edu | yaypcbs@mit.edu

## Let's use this circuit...

### ... and assume a footprint

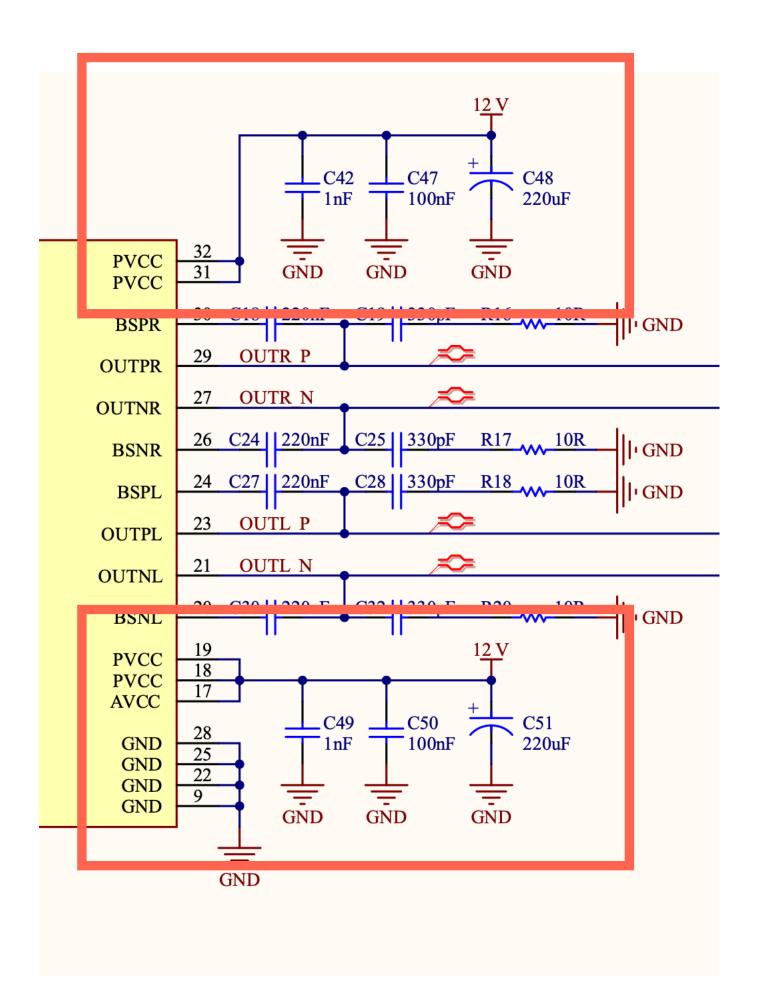

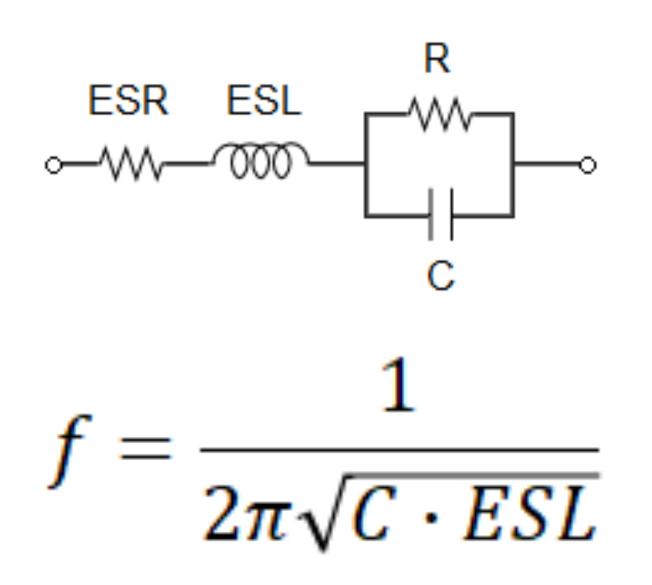

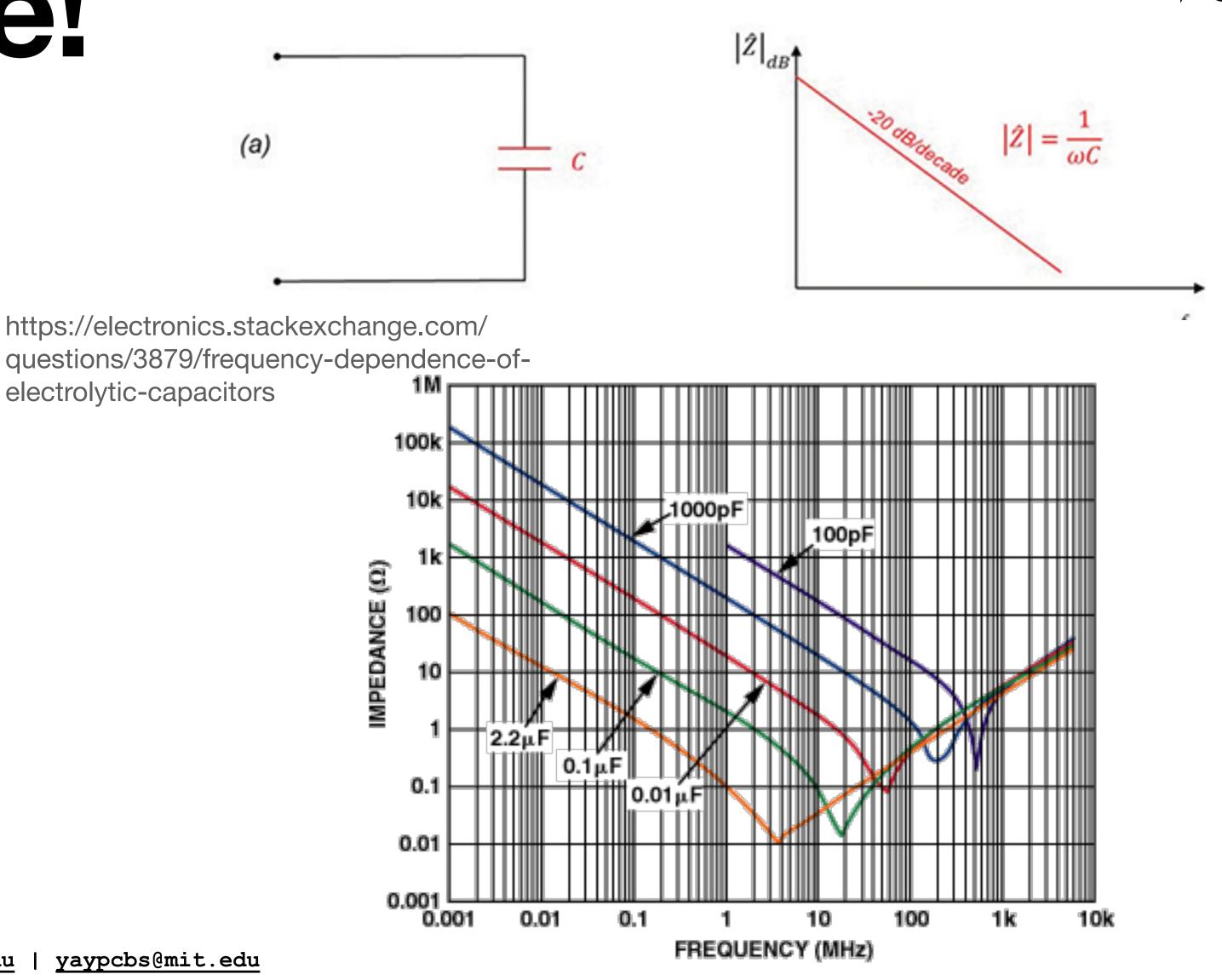

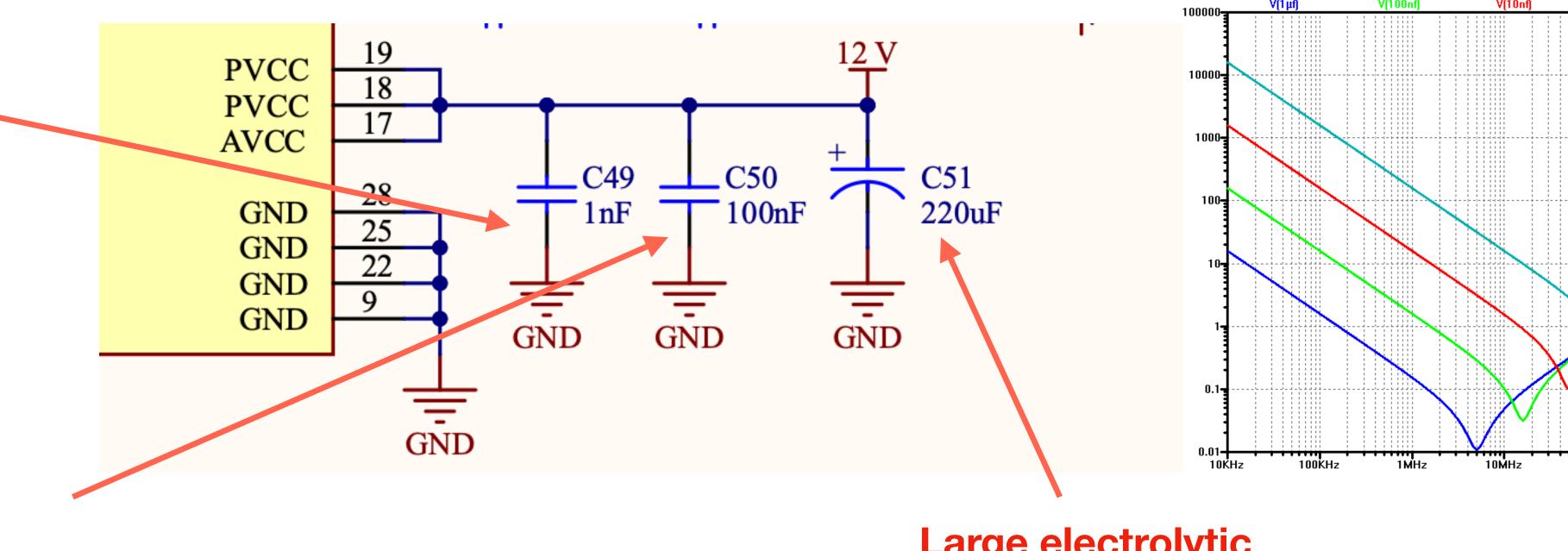

# What are these capacitors for? Why are they duplicates?

1/jw\*C

## ? Why ates?

# Bypass Capacitance!

(a)

https://electronics.stackexchange.com/ electrolytic-capacitors

https://resources.altium.com/p/what-sizedecoupling-capacitor-should-i-use-my-digital-ics

https://incompliancemag.com/article/ impact-of-a-trace-length-on-capacitorfrequency-response/

PCBDESIGN

### Bypass Capacitance!

**1nF** capacitor for super high frequency noise

### **100nF** capacitor for medium-high frequency noise

lecture 4 - Layout as an Art + Science | pcb.mit.edu | yaypcbs@mit.edu

**PCB** DESIGN

https://electronics.stackexchange.com/ questions/3879/frequencydependence-of-electrolytic-capacitors

Large electrolytic capacitor with high **ESR for low frequency** noise

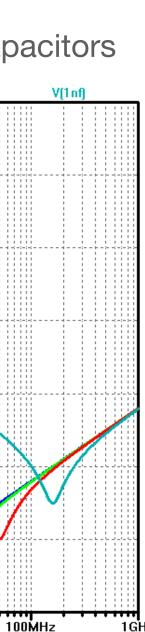

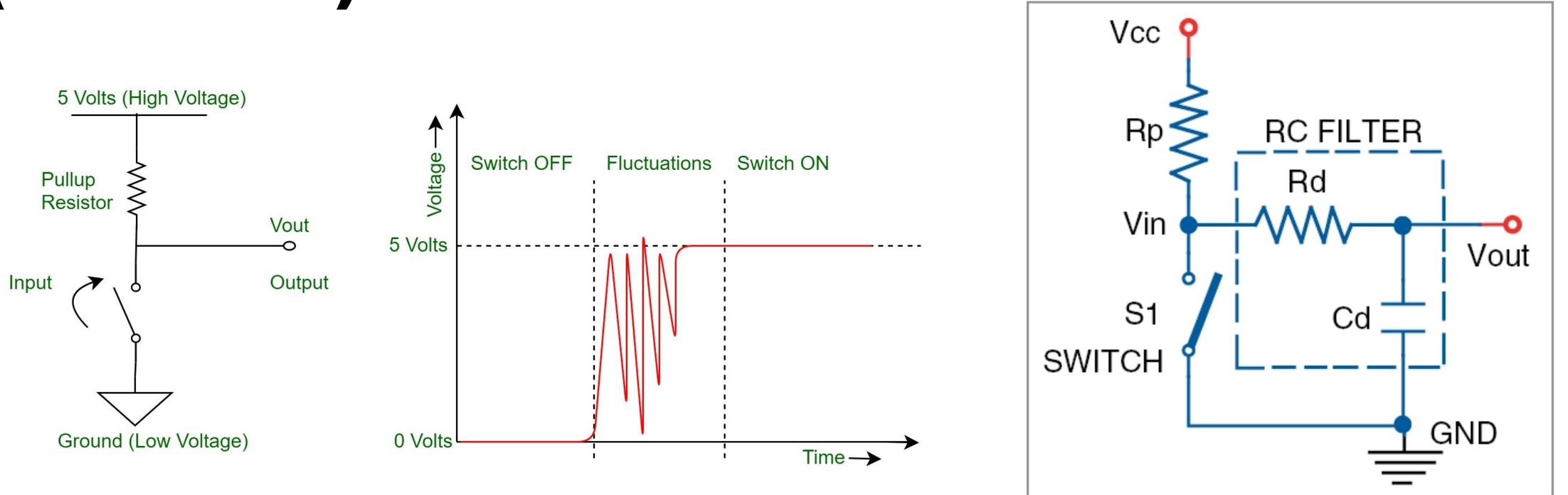

## Location of Bypass.

https://www.protoexpress.com/blog/decoupling-capacitor-placement-guidelines-pcb-design/

lecture 4 - Layout as an Art + Science | pcb.mit.edu | yaypcbs@mit.edu

https://www.protoexpress.com/blog/decoupling-capacitor-use/

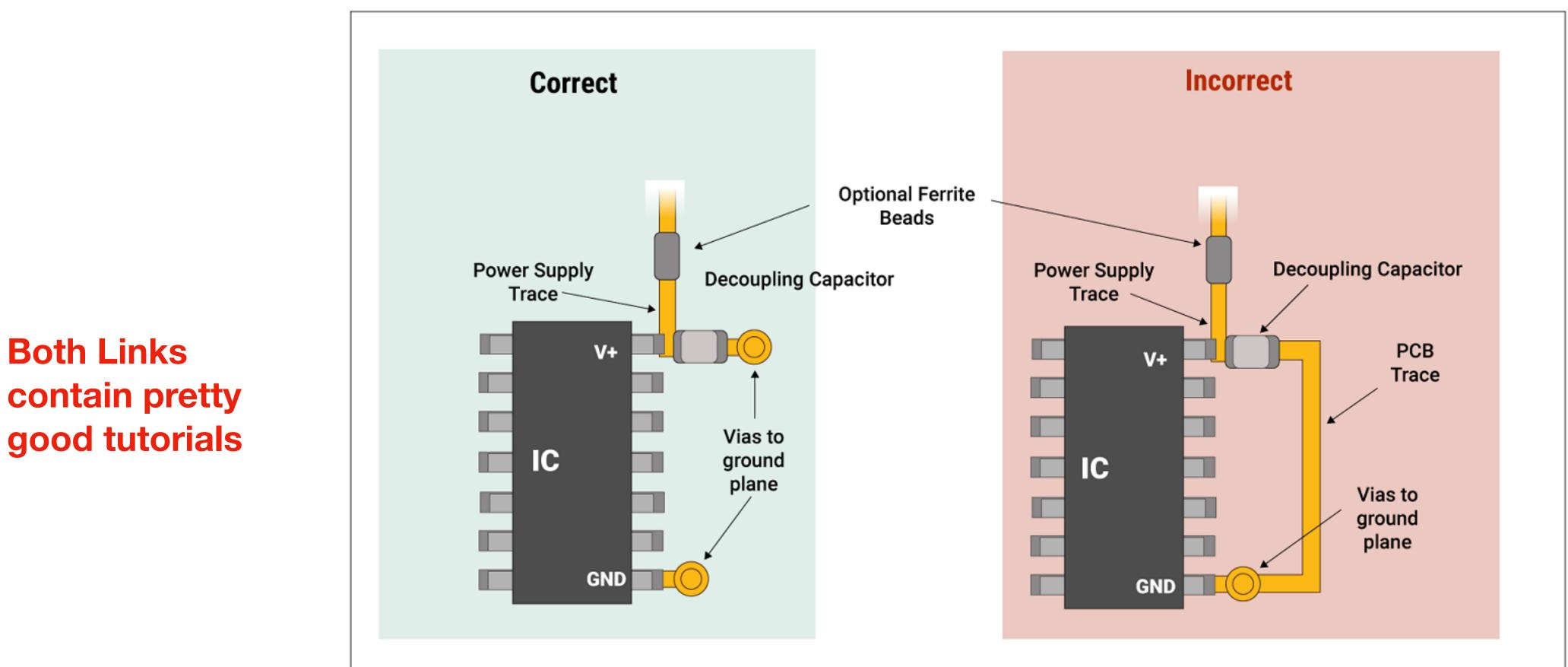

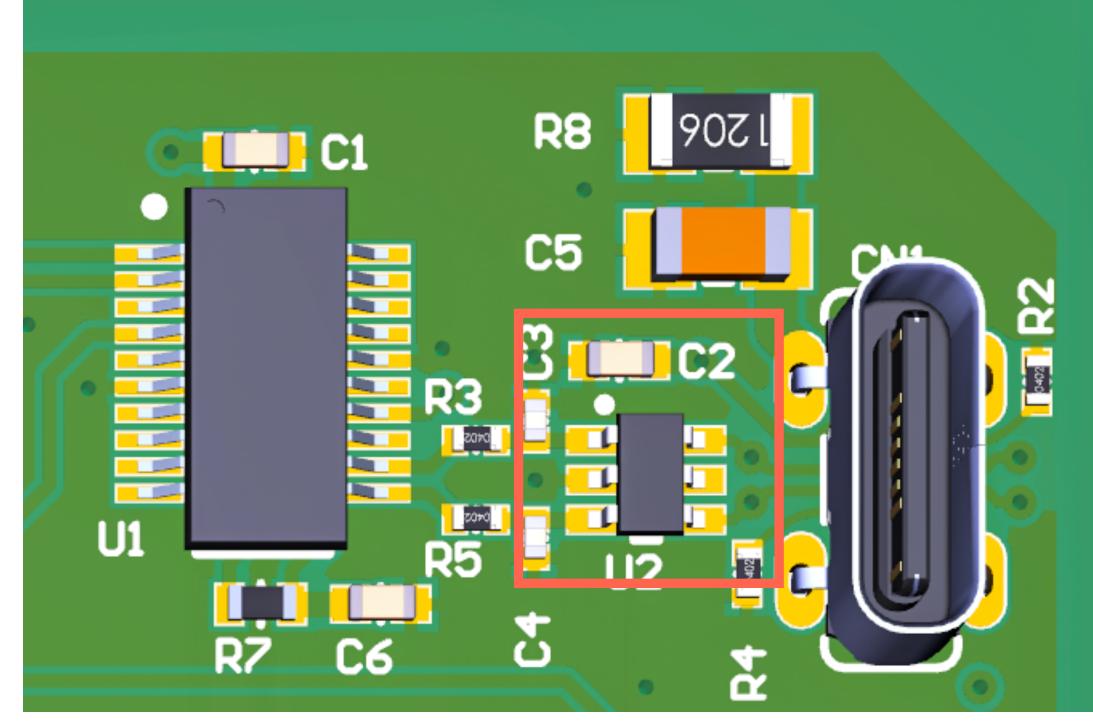

### Location for Filtration / Debounce (and ESD).

https://www.geeksforgeeks.org/switch-debounce-in-digital-circuits/

lecture 4 - Layout as an Art + Science | pcb.mit.edu | yaypcbs@mit.edu

https://www.electronicsforu.com/electronicsprojects/electronics-design-guides/switchdebouncer-working

# (Close to button)

### ESD.

# (Close to USB / port / etc)

WWW.INTEGRASOURCES.COM

https://www.integrasources.com/blog/electronics-design-practices-prevent-eosand-esd-damage/

lecture 4 - Layout as an Art + Science | pcb.mit.edu | yaypcbs@mit.edu

WWW.INTEGRASOURCES.COM

## What side of the board 'mate?

### Most of the time, keep each sub-circuit on the same side of the board.

### Manufacturing considerations as well.

lecture 4 - Layout as an Art + Science | pcb.mit.edu | yaypcbs@mit.edu

### For debugging or access or population you may only want components on one side of the board.

Still separate power and signal with X/Y distance, don't put power on one side right on top of signal.

### Routing the board, tools for connection?

### DO NOT USE AUTOROUTE. ITS BAD. ITS BAD. ITS BAD. IF YOU DON'T KNOW WHAT AUTOROUTE IS. GOOD. STAY INNOCENT.

lecture 4 - Layout as an Art + Science | pcb.mit.edu | yaypcbs@mit.edu

SCIE SCIE DCB

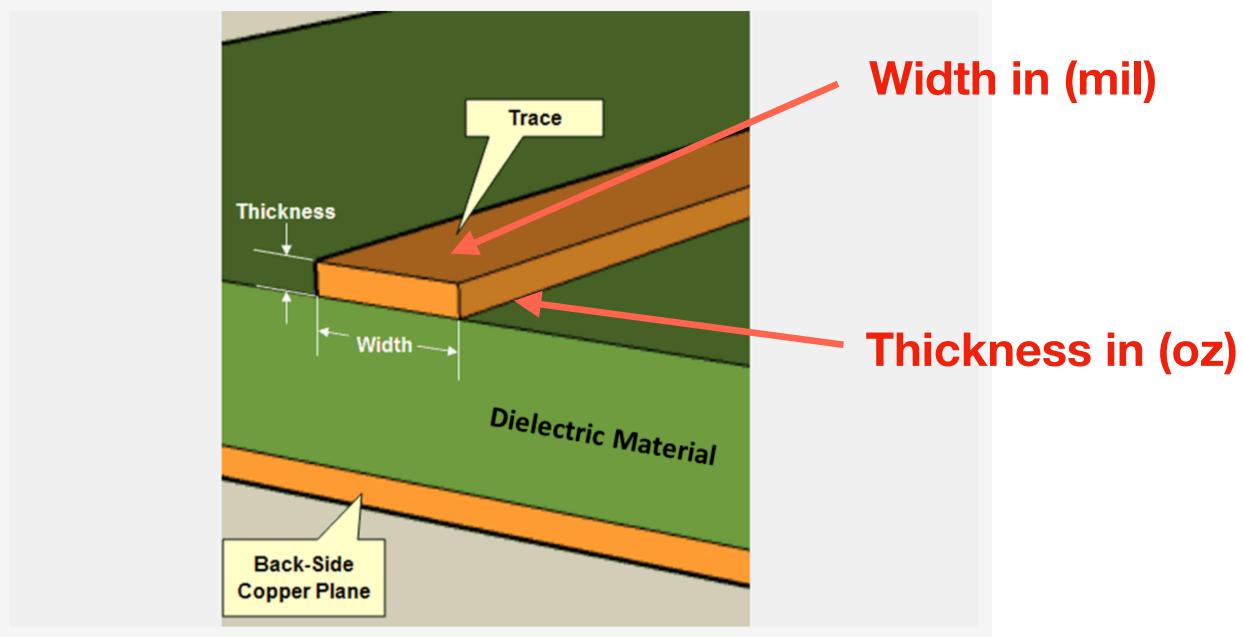

PCB trace structure

https://www.protoexpress.com/blog/trace-current-capacity-pcb-design/

lecture 4 - Layout as an Art + Science | pcb.mit.edu | yaypcbs@mit.edu

## PCRDESIGN

**1 oz Copper Thickness Conversion**

1 oz

1.37 mils (thousandths of an inch) \*To determine the thickness of 4 oz, simply multiply 1 oz thickness x 4. 0.00137 inch  $1.37 \text{ mil } x \ 4 = 5.48 \text{ mils} = 4 \text{ oz}$ 0.0347 mm

34.79  $\mu$ m (micron/micro meter)

https://www.pcbuniverse.com/pcbu-tech-tips.php?a=4

https://www.mclpcb.com/blog/pcb-trace-width-vs-current-table/

IPC Recommended Track Width For 1 oz cooper PCB and 10 °C Temperature Rise

| Current/A | Track Width(mil) | Track Width(mm) |  |

|-----------|------------------|-----------------|--|

|           |                  |                 |  |

| 1         | 10               | 0.25            |  |

| 2         | 30               | 0.76            |  |

| 3         | 50               | 1.27            |  |

| 4         | 80               | 2.03            |  |

| 5         | 110              | 2.79            |  |

| 6         | 150              | 3.81            |  |

| 7         | 180              | 4.57            |  |

| 8         | 220              | 5.59            |  |

| 9         | 260              | 6.60            |  |

| 10        | 300              | 7.62            |  |

### Max Current

You can calculate maximum current by using the formula  $A = (T \times W \times 1.378 \text{ [mils/oz/ft}^2\text{]}).$

The values in this formula correspond with the following parameters:

- A: Cross-section area.

- [mils2] T: Trace thickness.

- [oz/ft2] W: Trace width.

Once you've worked through the previous equation, you'll determine the maximum current using  $I_{MAX} = (k \times T_{RISE}^{b}) \times A^{c}$ . The fields for this formula are as follows:

- [mils] I<sub>MAX</sub>: Maximum current.

- [A] TRISE: Maximum desired temperature rise.

- [°C] k, b and c: Constants.

https://www.mclpcb.com/blog/pcb-trace-width-vs-current-table/

IPC Recommended Track Width For 1 oz cooper PCB and 10 °C Temperature Rise

| Current/A | Track Width(mil) | Track Width(mm) |  |

|-----------|------------------|-----------------|--|

|           |                  |                 |  |

| 1         | 10               | 0.25            |  |

| 2         | 30               | 0.76            |  |

| 3         | 50               | 1.27            |  |

| 4         | 80               | 2.03            |  |

| 5         | 110              | 2.79            |  |

| 6         | 150              | 3.81            |  |

| 7         | 180              | 4.57            |  |

| 8         | 220              | 5.59            |  |

| 9         | 260              | 6.60            |  |

| 10        | 300              | 7.62            |  |

### **Resistance Calculation**

When calculating trace resistance in your PCB, you'll begin by converting the cross-section area from [mils<sup>2</sup>] to [cm<sup>2</sup>] following the formula A' = A \*  $2.54 * 2.54 * 10^{-6}$ .

The values in these formulas correspond with the following quantities:

- [oz/ft<sup>2</sup>] W: Trace width.

- [mils] R: Trace resistance.

- [Ω] ρ: Resistivity parameter.

- $[\Omega \cdot cm]$  L: Trace length.

- **[cm]** α: Resistivity temperature coefficient.

- [1/°C] <sup>T</sup><sub>TEMP</sub>: Trace temperature.

After working through the equation, you'll quantify the trace resistance using R = ( $\rho * L / A'$ ) \* (1 +  $\alpha * (^{T}_{TEMP} - 25 °C)$ ).

• T: Trace thickness.

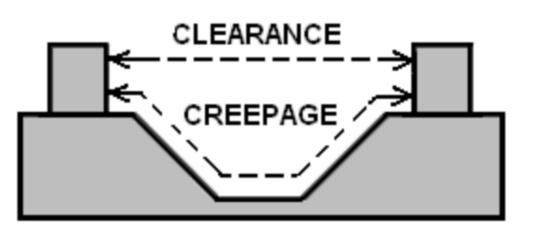

https://www.smps.us/pcbtracespacing.html

Electrical clearances and creepage for various types of insulation for mains up to 250VAC and working voltages up to 420V

|           | Functional | Basic | Reinforced |

|-----------|------------|-------|------------|

| Clearance | 1.5        | 2     | 4          |

| Creepage  | 3.2        | 3.2   | 6.4        |

Functional insulation- primary to primary and secondary to secondary; Basic insulation- primary to chassis; Reinforced insulation- primary to secondary. http://www.smps.us/ kV/cm

### At atmospheric pressure, the breakdown strength of air is ~30

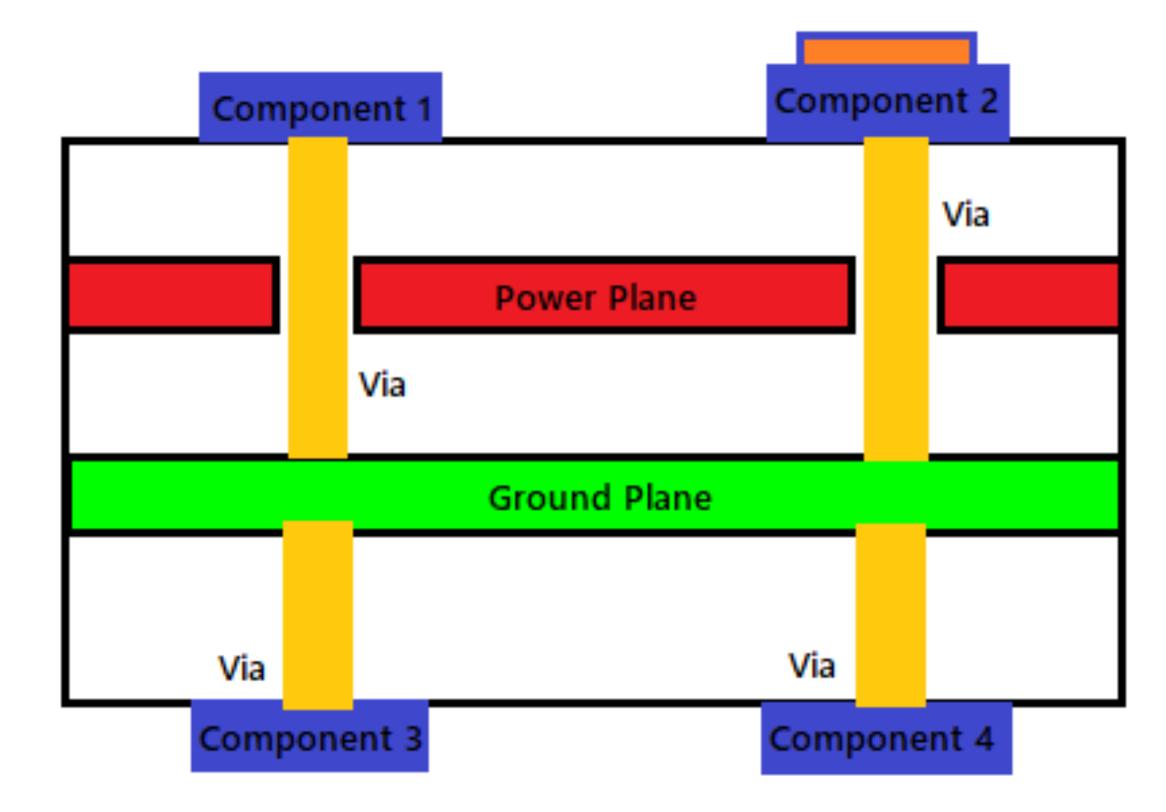

### **Planes + the Layer-**Stack-Manager.

https://www.onelectrontech.com/pcb-layout-design-tips-grounding-considerations/

lecture 4 - Layout as an Art + Science | pcb.mit.edu | yaypcbs@mit.edu

https://welldoneblog.fedevel.com/2013/09/11/online-advanced-pcb-layoutcourse-by-motherboard-designer/

### Planes + the Layer-Stack-Manager.

# (Start w/ 2 layers and then increase as needed)

## Vias.

### Pretty common practice w/ signals going to a microcontroller.

### **Used to transition** from layer to layer.

lecture 4 - Layout as an Art + Science | pcb.mit.edu | yaypcbs@mit.edu

### SCIENCE PCBDESIGN

### https://

electronics.stackexchange.co m/questions/604828/routingtraces-to-and-from-a-48-pinmicrocontroller-becoming-amess

## Pours, Pads, Polygons.

**Better than** running massive traces. Good way to get power around in a 2-layer board.

lecture 4 - Layout as an Art + Science | pcb.mit.edu | yaypcbs@mit.edu

## PCBDESIGN

### Layout considerations, capacitors, debugging, parasitics.

### Trace Shapes, Sharp Turns, EMI

https://resources.altium.com/p/pcb-routing-angle-myths-45-degree-angle-versus-90-degree-angle

lecture 4 - Layout as an Art + Science | pcb.mit.edu | yaypcbs@mit.edu

**Engineers are often concerned about having right-angle PCB** tracks on their circuit board shape due to the possibility of **Electromagnetic Interference (EMI) radiated at sharp corners.** The popular theory is that high-frequency signals emit Radio Frequency radiation at every 90° turn of the copper track. This mere assumption is enough for most hardware designers to eliminate any right-angle PCB routing from their track design or auto router software.

There is an exception--when you're designing ultra high-speed PCB ground plane in the range of 10 GHz or more, or you're involved in microwave designs that use traces with large widths of 100 mils. In such extreme applications, you actually need to worry about 90° corners. Otherwise, they should not present a major concern.

#### But the 45 deg corners do make a nicer looking board.

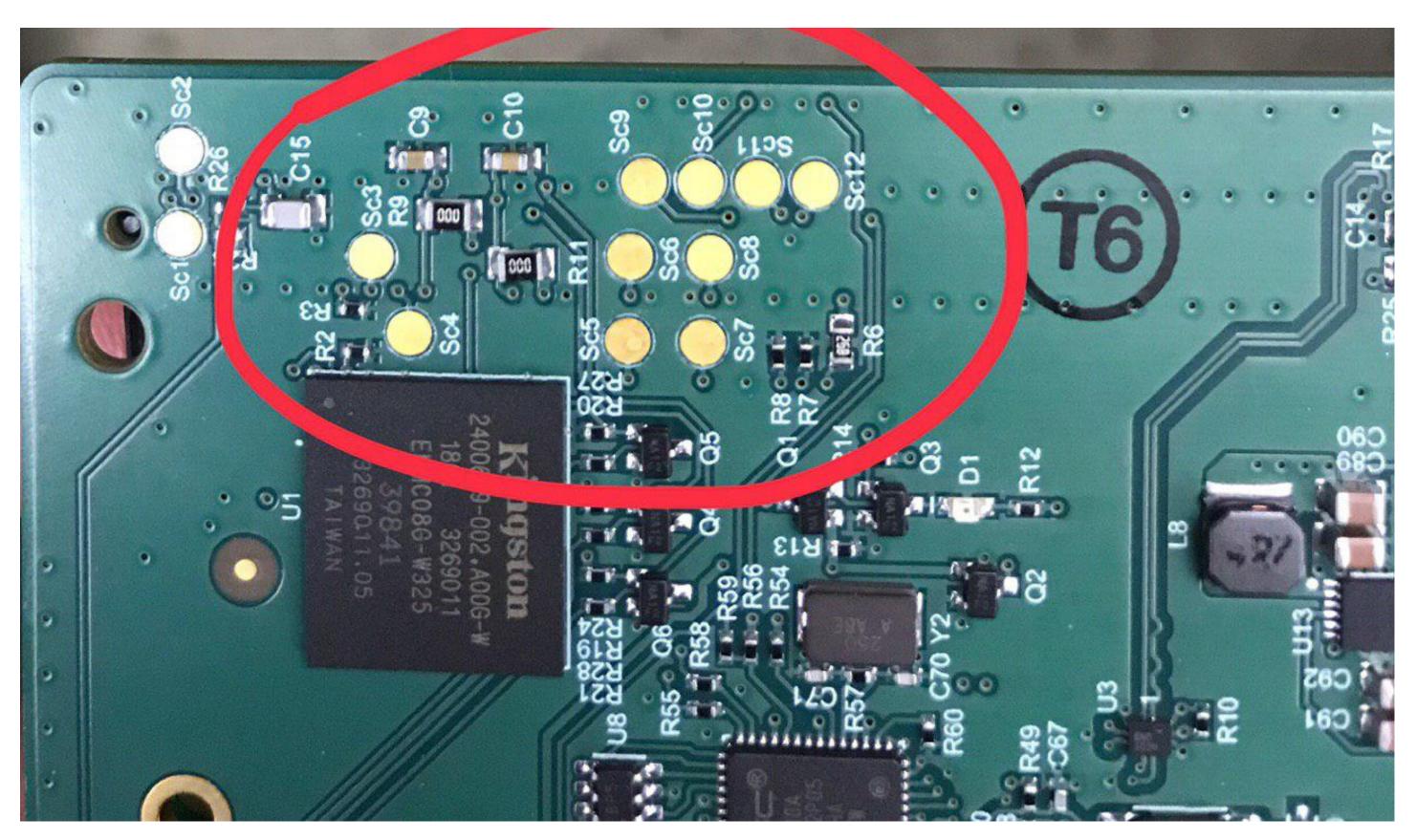

#### Debugging Considerations + Breakouts.

https://www.reddit.com/r/diyelectronics/comments/nynup4/any\_way\_to\_permanently\_connect\_to\_a\_pcb\_test\_pad/

lecture 4 - Layout as an Art + Science | pcb.mit.edu | yaypcbs@mit.edu

# These are called TEST POINTS!

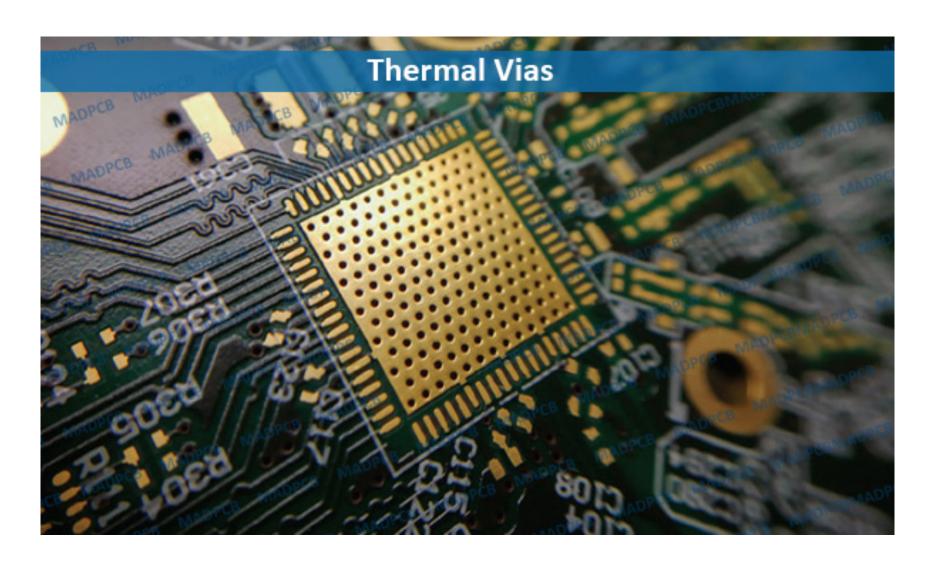

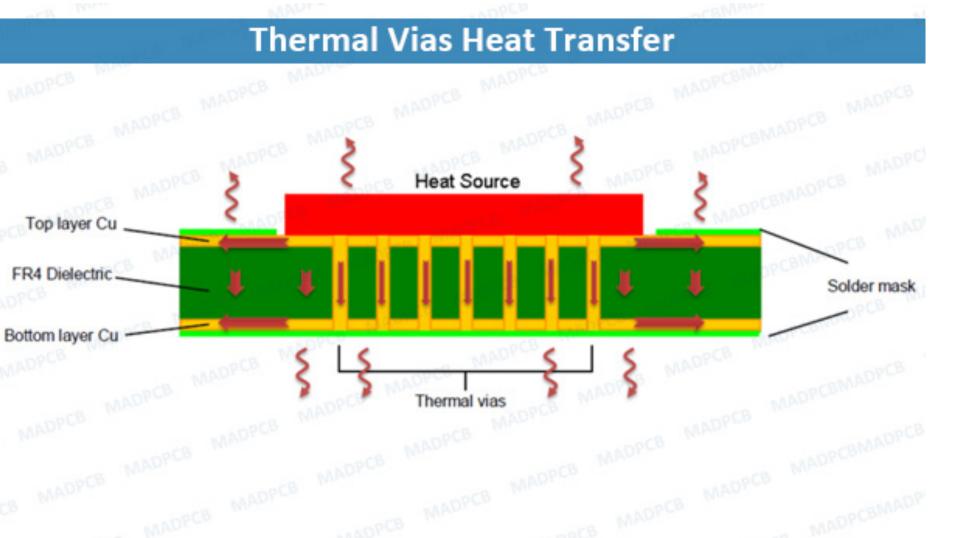

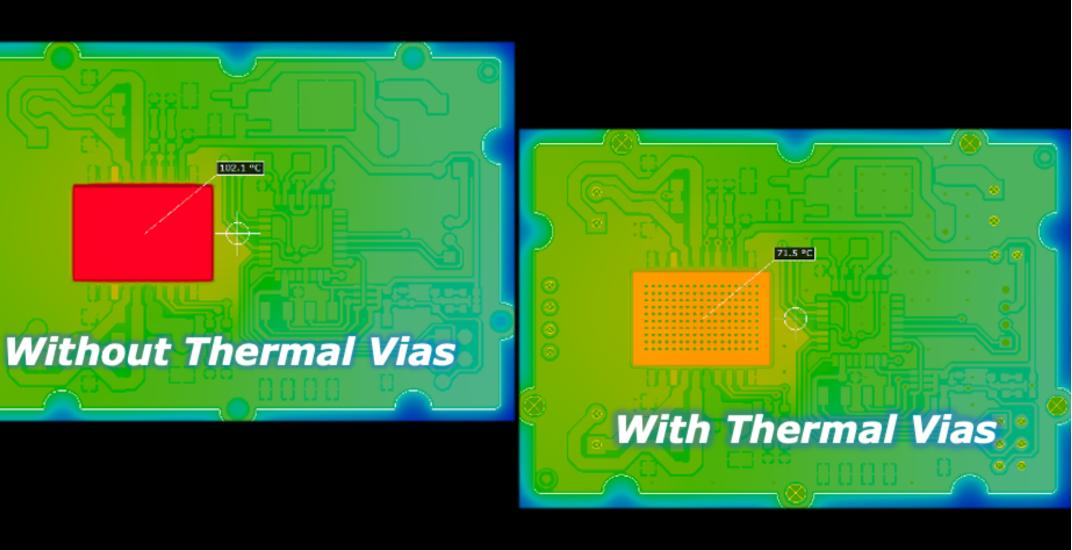

### Thermals.

https://madpcb.com/glossary/thermal-vias/

lecture 4 - Layout as an Art + Science | pcb.mit.edu | yaypcbs@mit.edu

https://www.linkedin.com/pulse/thermal-vias-benefitslimitations-günther-schindler/

SCIENCE DCB DESIGN

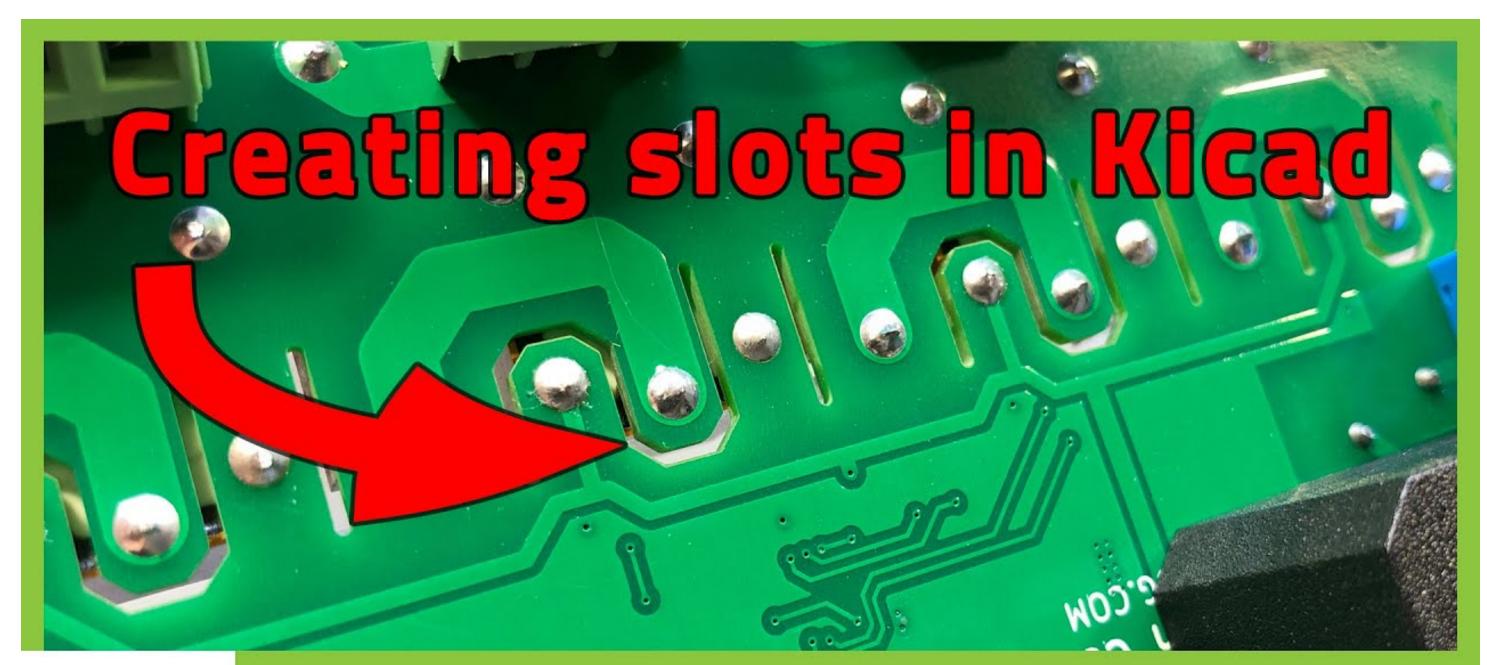

## Isolation.

#### VoltLog #364 How To Create High Voltage Isolation Slots In Kicad

lecture 4 - Layout as an Art + Science | pcb.mit.edu | yaypcbs@mit.edu

<u>youtube.com/watch?v=BAJZpNDjilA</u>

#### For separating large voltages over small distances we can use SLOTS in PCBs! This gives better isolation.

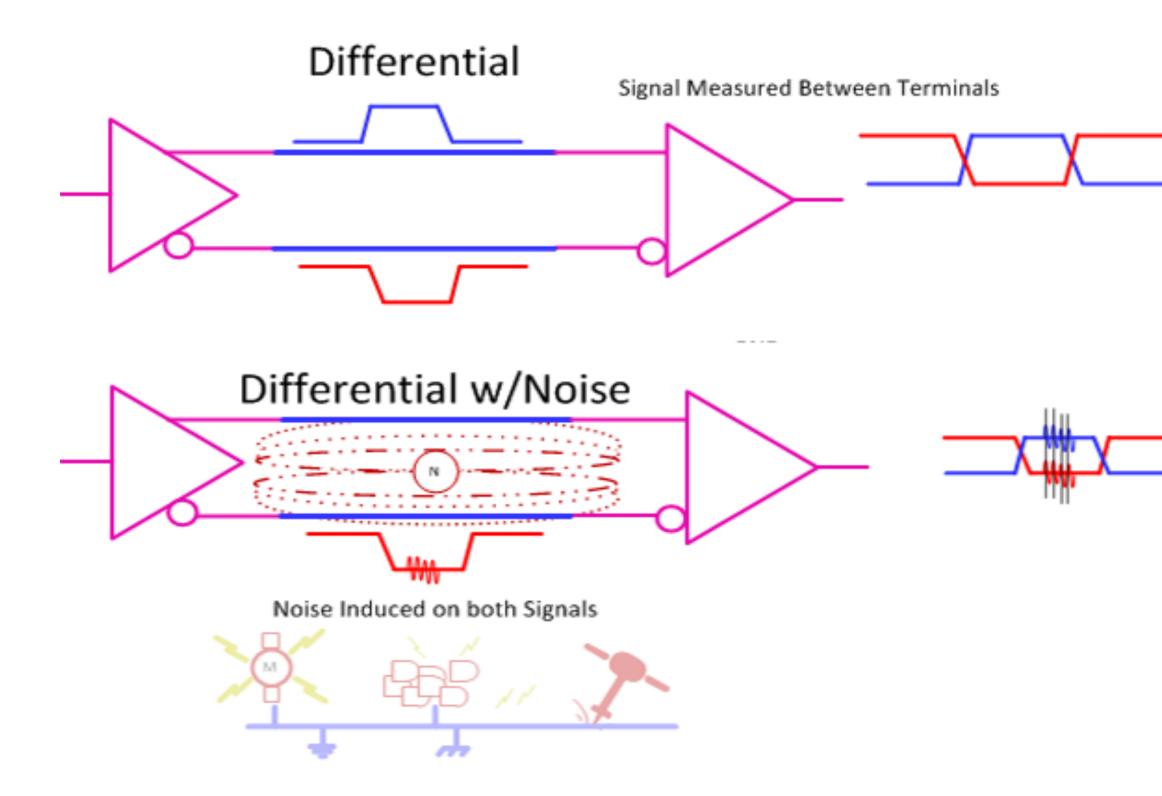

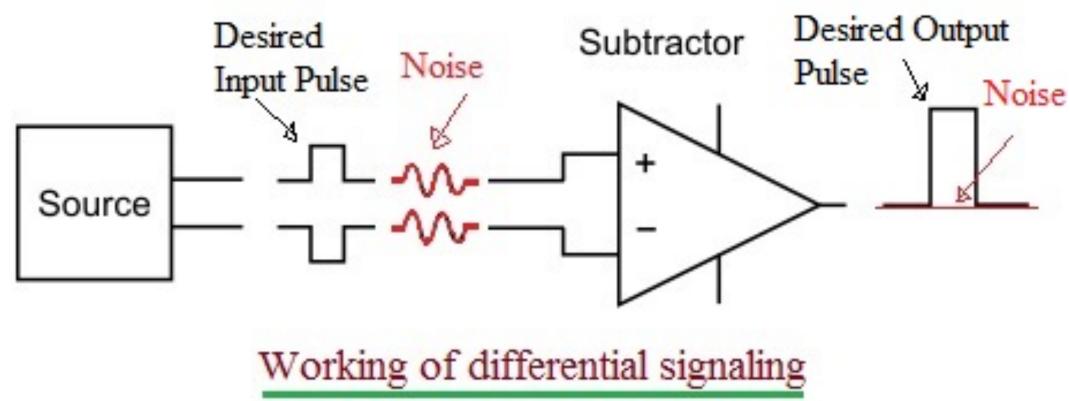

### **Differential Pairs** + Signal Integrity.

https://hackaday.com/2016/03/29/when-difference-matters/

lecture 4 - Layout as an Art + Science | pcb.mit.edu | yaypcbs@mit.edu

#### SCIED **PC**R DESIGN

https://www.rfwireless-world.com/Terminology/Advantages-and-Disadvantages-of-differential-signaling.html

### Connectors.

## Connectors should lie at the edge of the board

Mechanical Interlocking Connectors - connector takes forces, pins transmit signal

#### Connectors is a whole science —> <u>https://</u> www.rbracing-rsr.com/wiring ecu.html

## (Race-spec series)

#### NO WIRES OVER THE BOARD!!!

#### Manufacturing Considerations + Board Shape.

#### Cost —> layers add cost

#### Size —> size adds cost

lecture 4 - Layout as an Art + Science | pcb.mit.edu | yaypcbs@mit.edu

#### Automated population —> two sided is more expensive than one sided

## Trace spacing and width —> also factors

#### Manufacturing **Considerations** + **Board Shape.**

lecture 4 - Layout as an Art + Science | pcb.mit.edu | yaypcbs@mit.edu

## PCRDESIGN

https://www.eurocircuits.com/pcb-design-guidelines/edge-connectors/

#### Mechanical Layers, Labeling, Naming, Blaming.

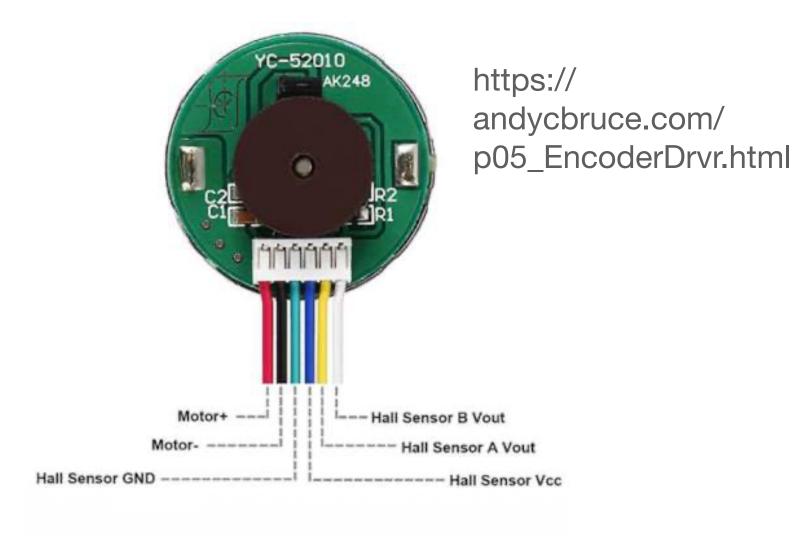

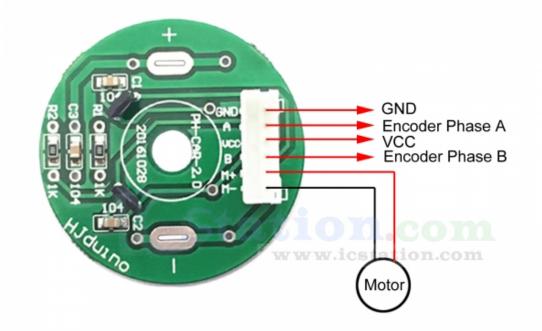

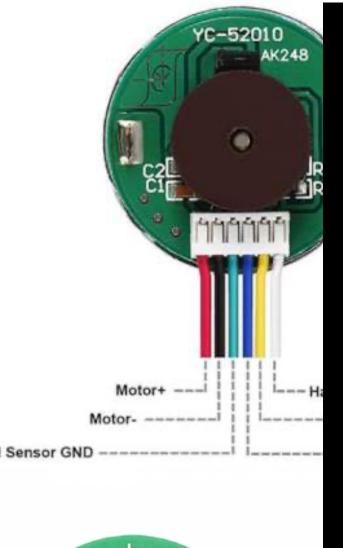

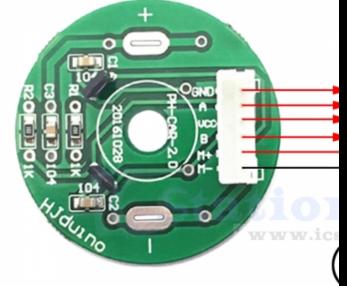

https://www.icstation.com/motorphase-incremental-hall-sensorencoder-magnetic-coding-speedmodule-control-p-16006.html

lecture 4 - Layout as an Art + Science | pcb.mit.edu | yaypcbs@mit.edu

SCIENCE **PCB** DESIGN

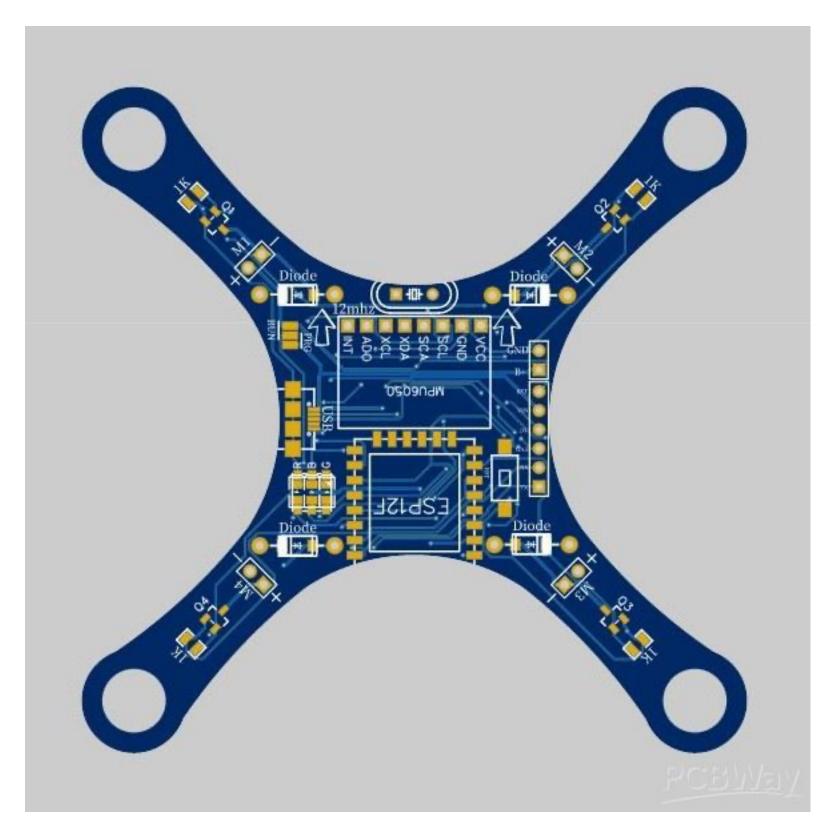

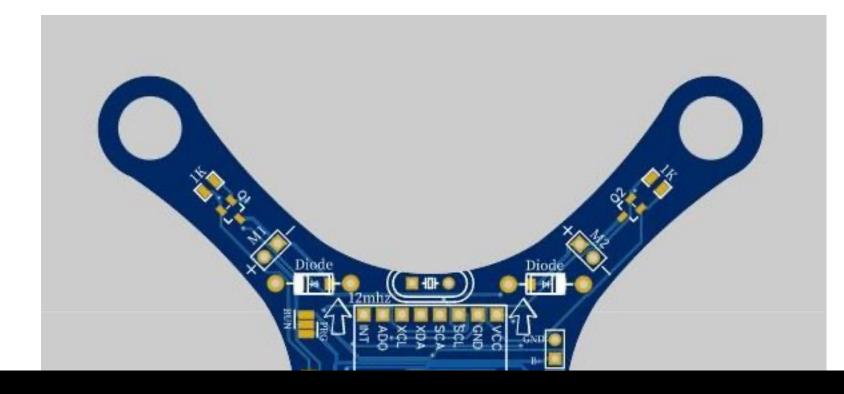

https://www.pcbway.com/ blog/PCB\_Design\_Tutorial/ How\_To\_Create\_PCB\_For\_ Drone.html

youtube.com/watch?v=-**BDCmwNssiw**

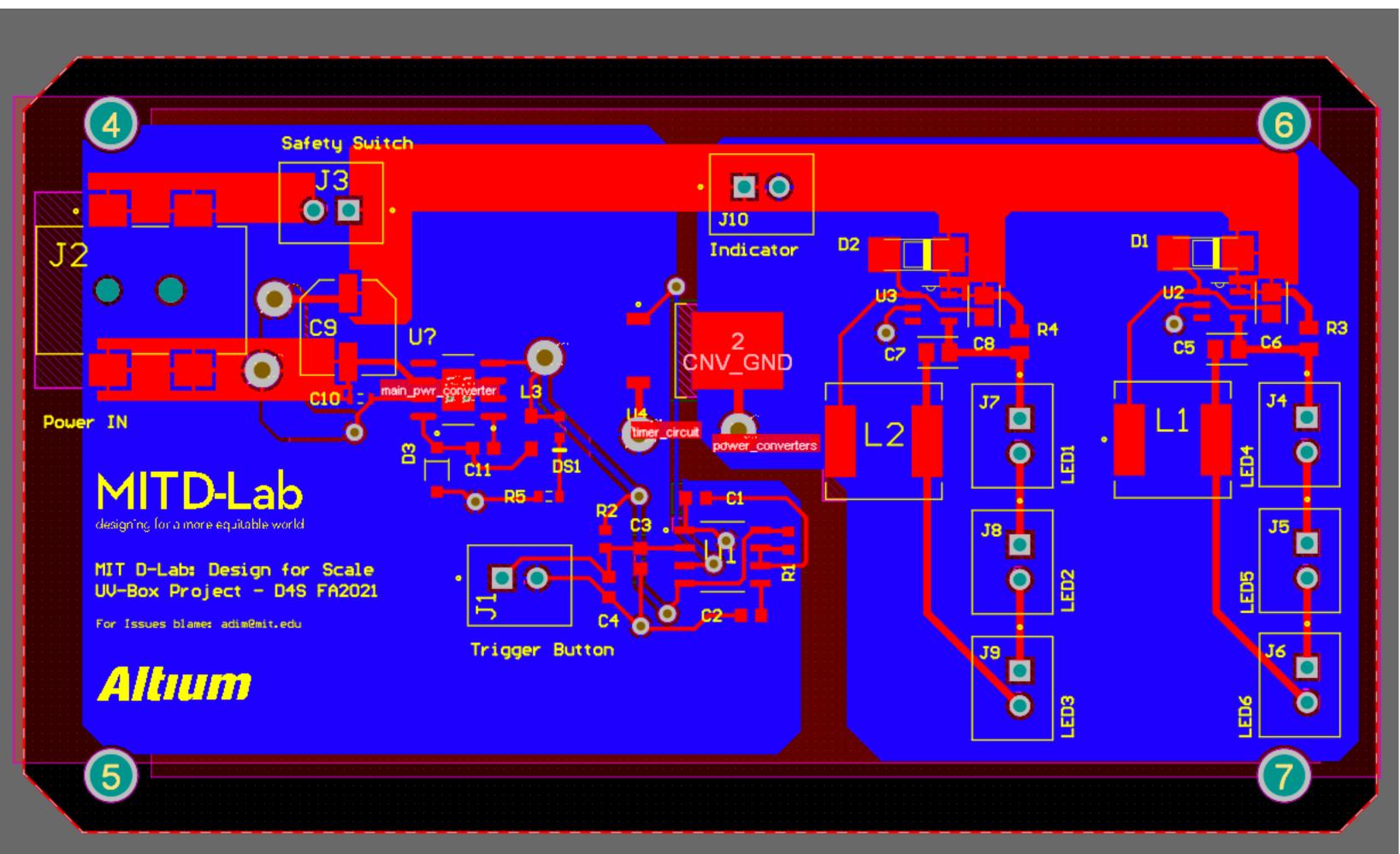

#### Mechanical Layers, Labeling, Naming, Blaming.

#### Tradition is to put your name and email on a PCB if you've made it so the person debugging it knows who to blame when it goes wrong ;D

lecture 4 - Layout as an Art + Science | pcb.mit.edu | yaypcbs@mit.edu

https://www.pcbway.com/

watch?v=-

# **Layout case studies,** a few boards (simple to complex).

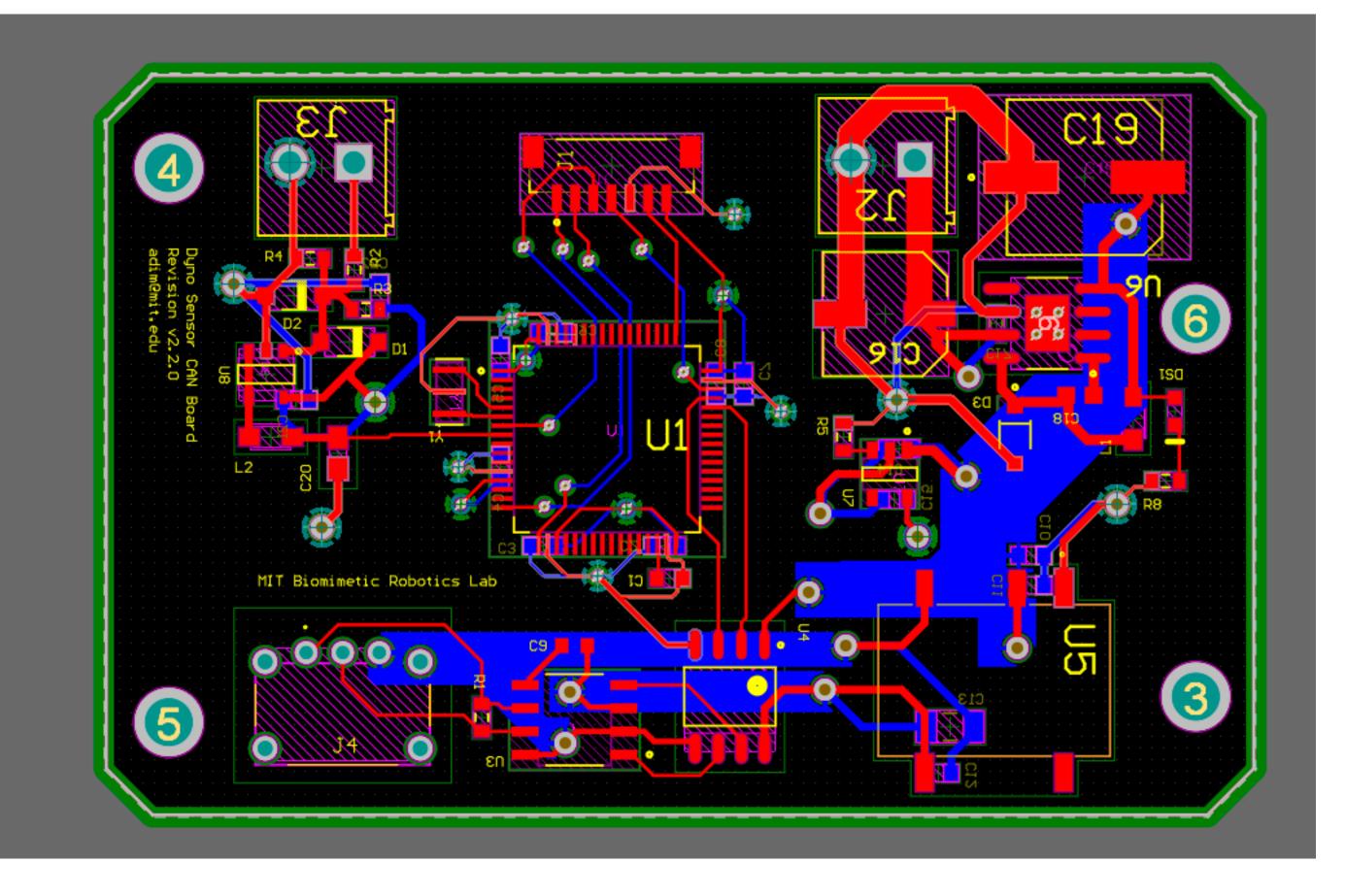

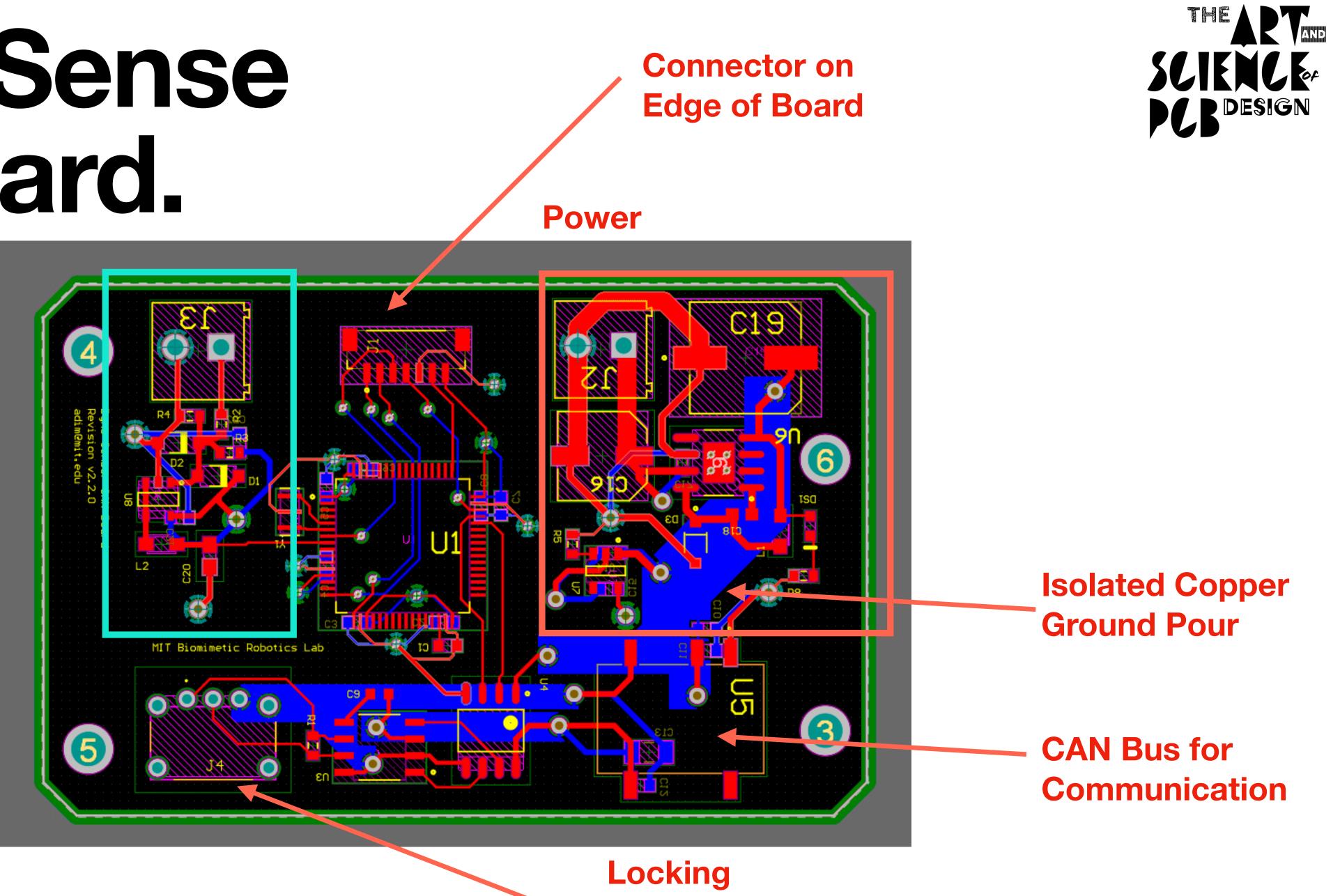

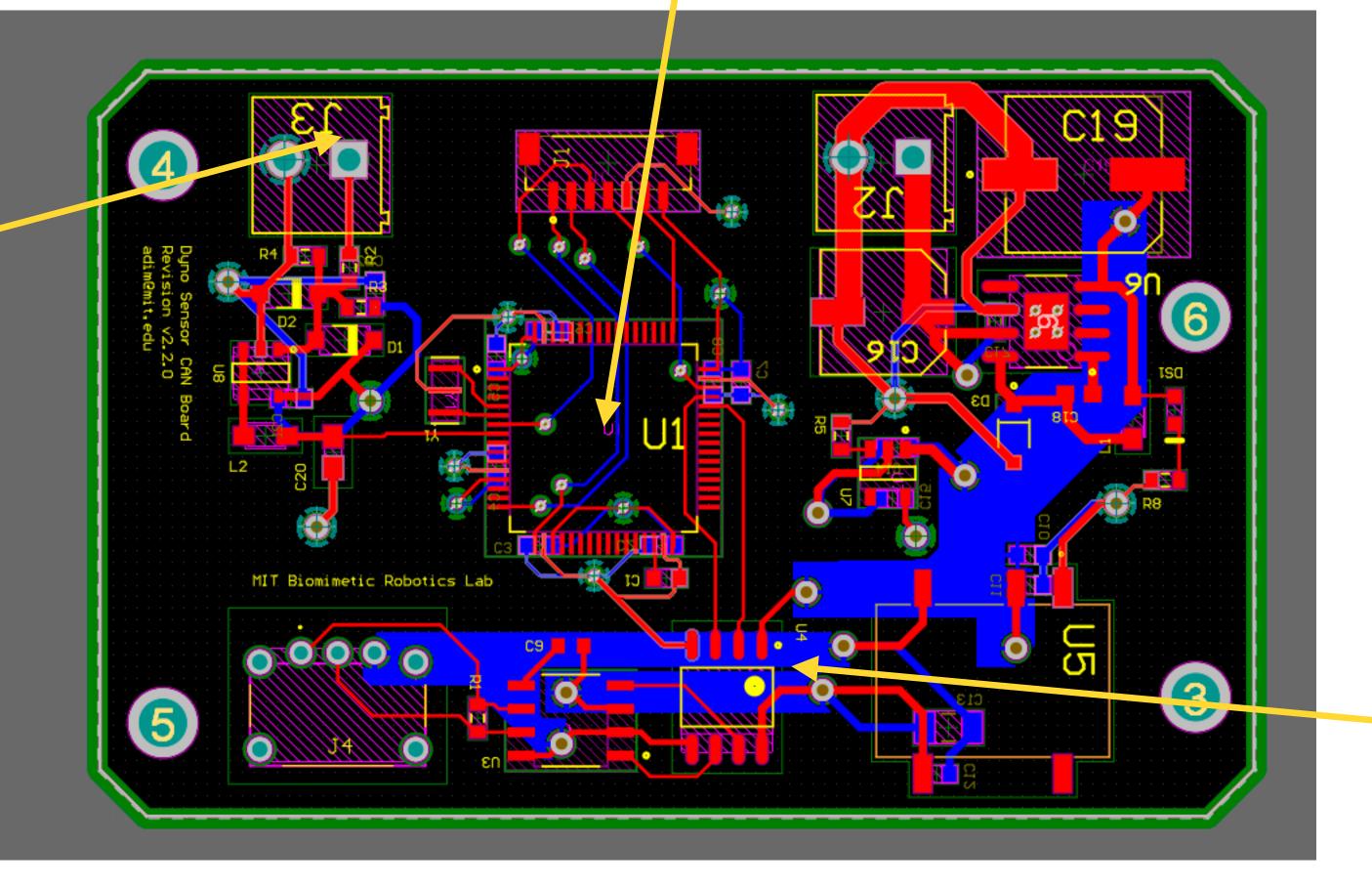

### Torque-Sense CAN Board.

### **Torque-Sense** CAN Board.

#### Super tight Analog signal routing

lecture 4 - Layout as an Art + Science | pcb.mit.edu | yaypcbs@mit.edu

**Connector for** CAN

## **Torque-Sense** CAN Board.

**SCREW TERMINAL FOR SENSOR, COULD BE BETTER**, **SCREW TERMINALS** HAVE A RESISTANCE

lecture 4 - Layout as an Art + Science | pcb.mit.edu | yaypcbs@mit.edu

#### **BAD** —> **BYPASS UNDER** THE BOARD, SHOULD BE **ON TOP**

#### $BAD \longrightarrow CAN$ NOT ROUTED AS **A DIFF PAIR**

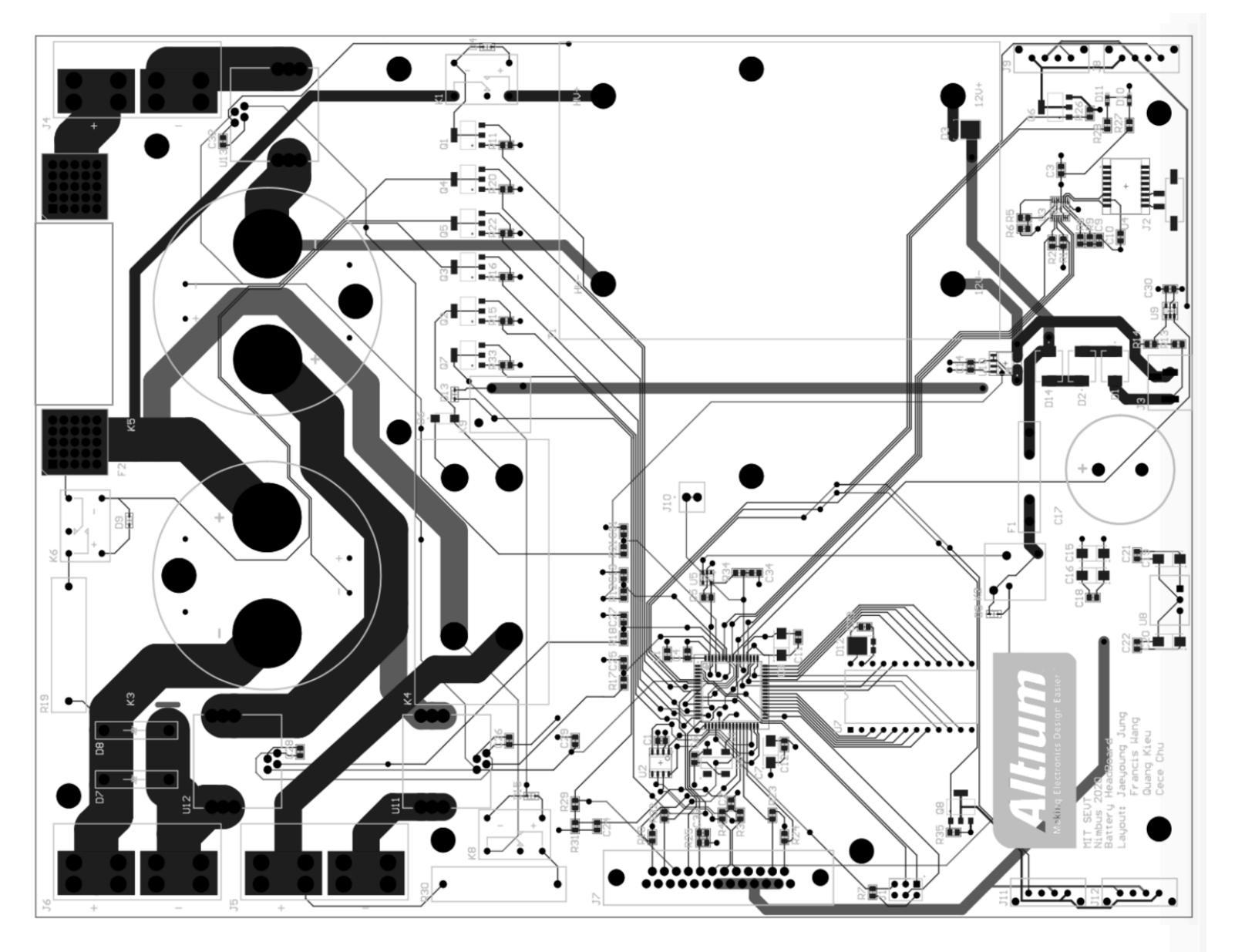

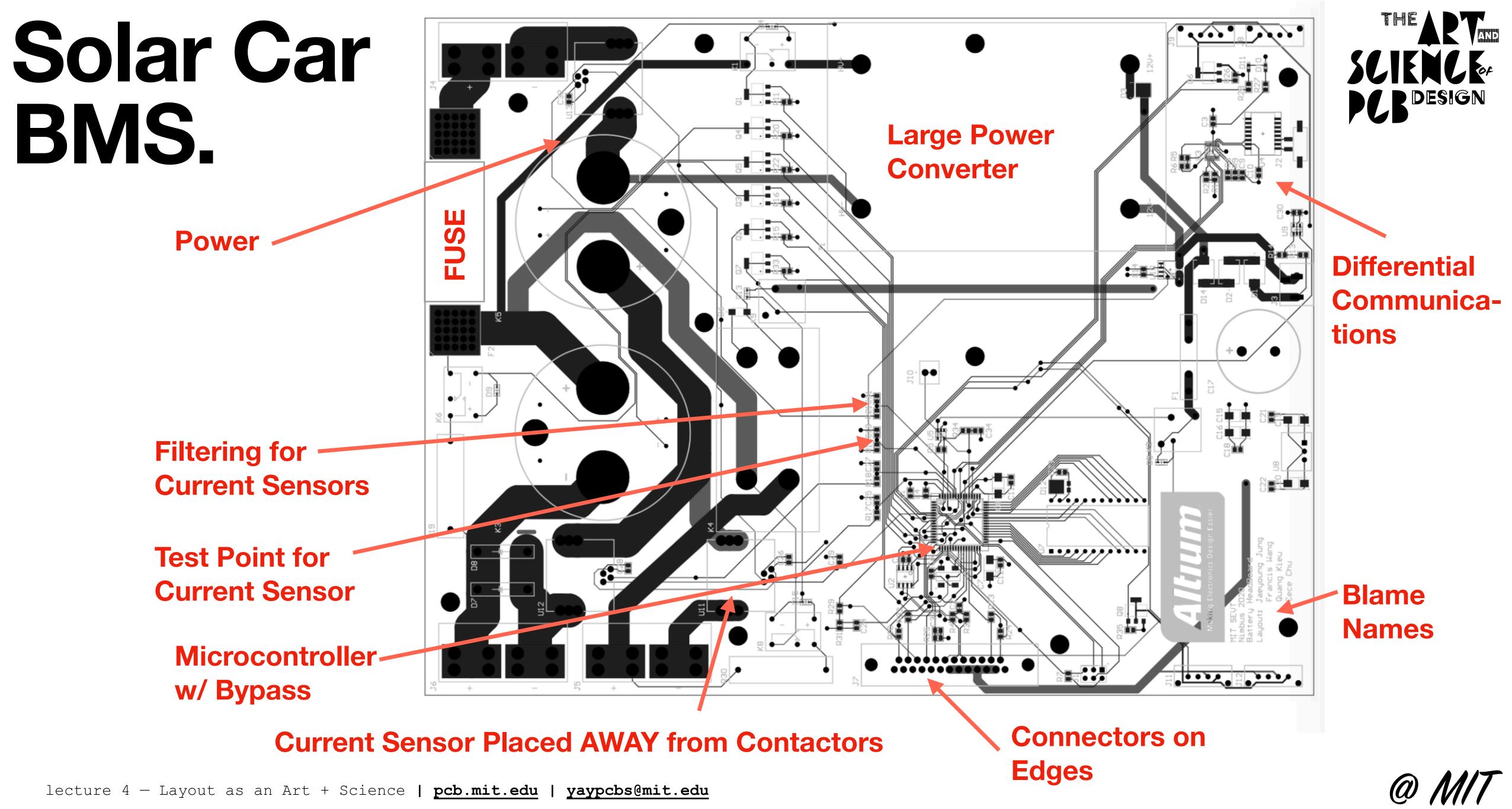

#### Solar Car BMS.

lecture 4 - Layout as an Art + Science | pcb.mit.edu | yaypcbs@mit.edu

## DESIGN

#### Solar Car BMS.

(Probably OK because of transmission speeds but diff pair is always better)

#### **Could probably have used** copper pours instead of large traces

lecture 4 - Layout as an Art + Science | pcb.mit.edu | yaypcbs@mit.edu

## **CB**DESIGN

**ISO-SPI** NOT **ROUTED AS A DIFF** PAIR

#### **CAN BUS NOT ROUTED AS A DIFF PAIR**

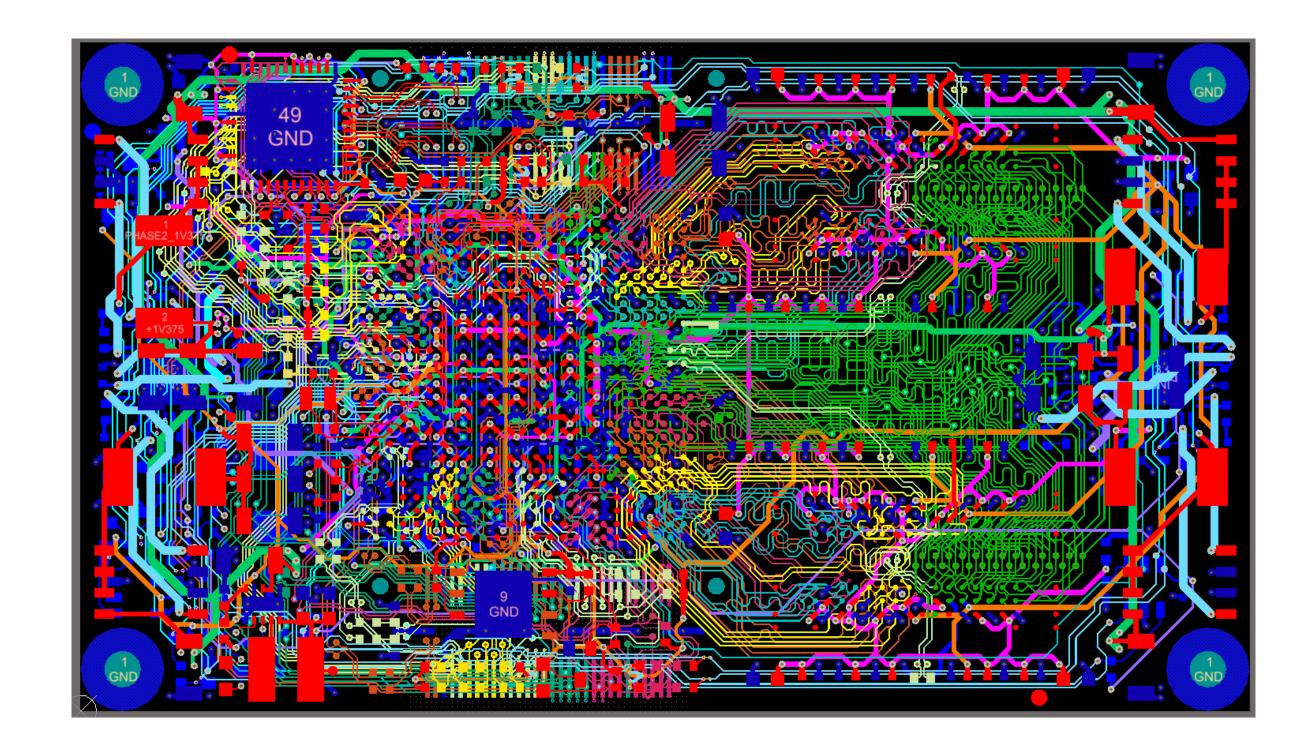

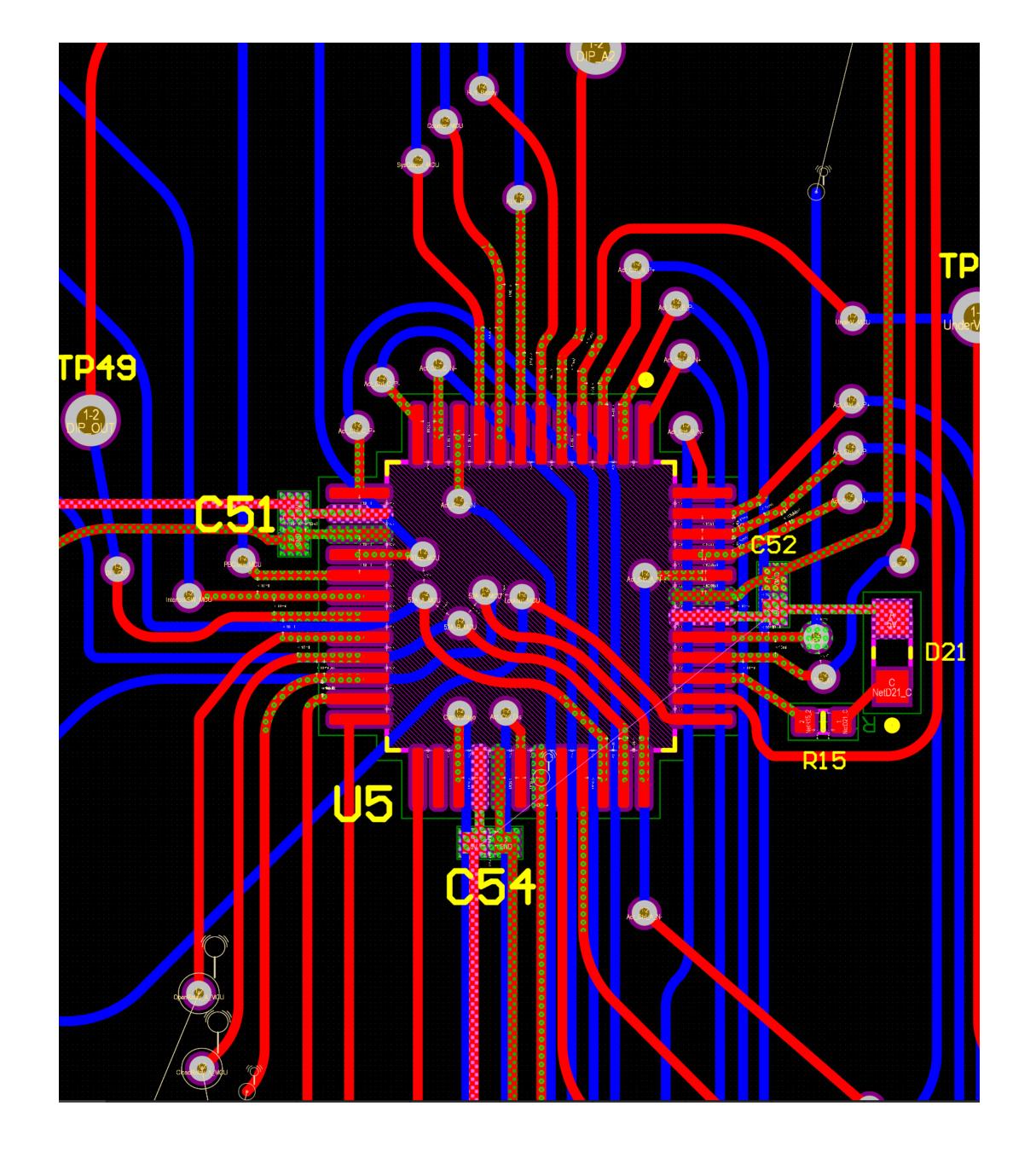

# **Detailed case study,** Ben Katz motor controller in Eagle.

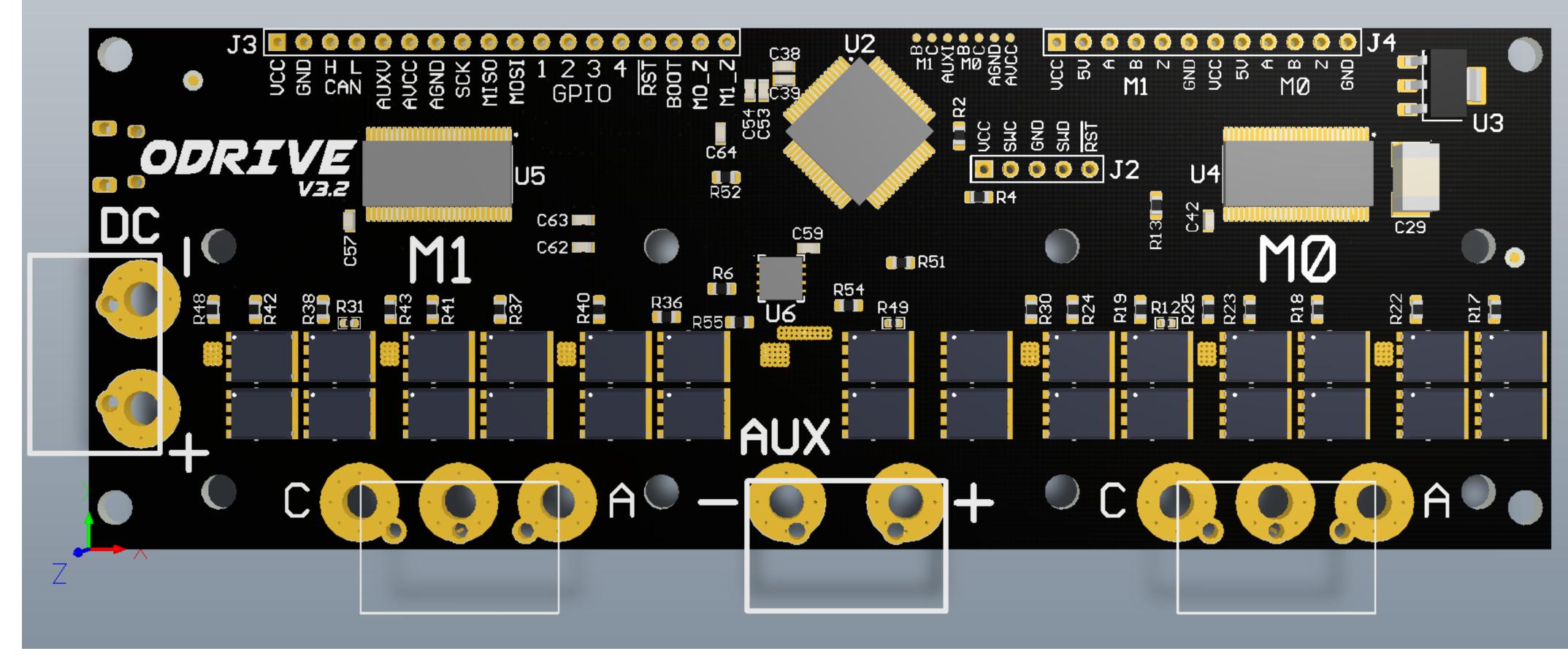

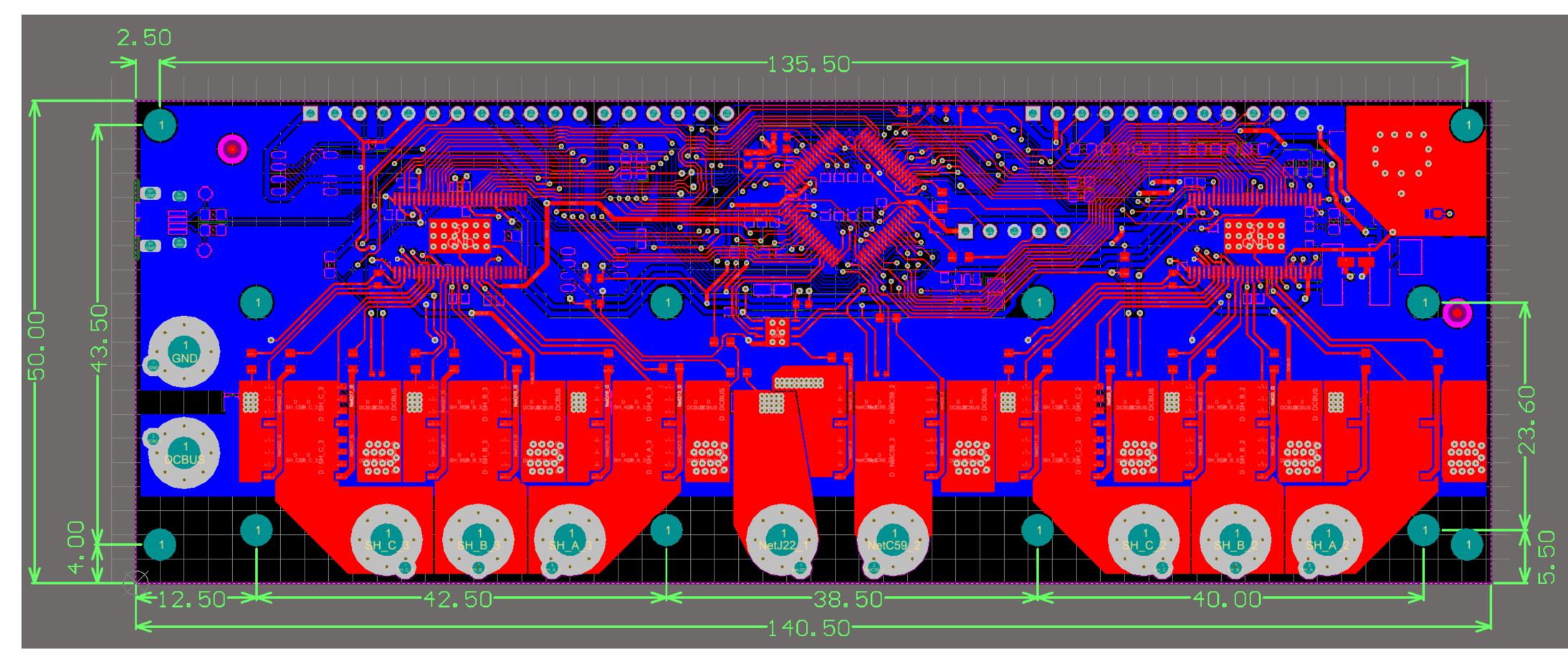

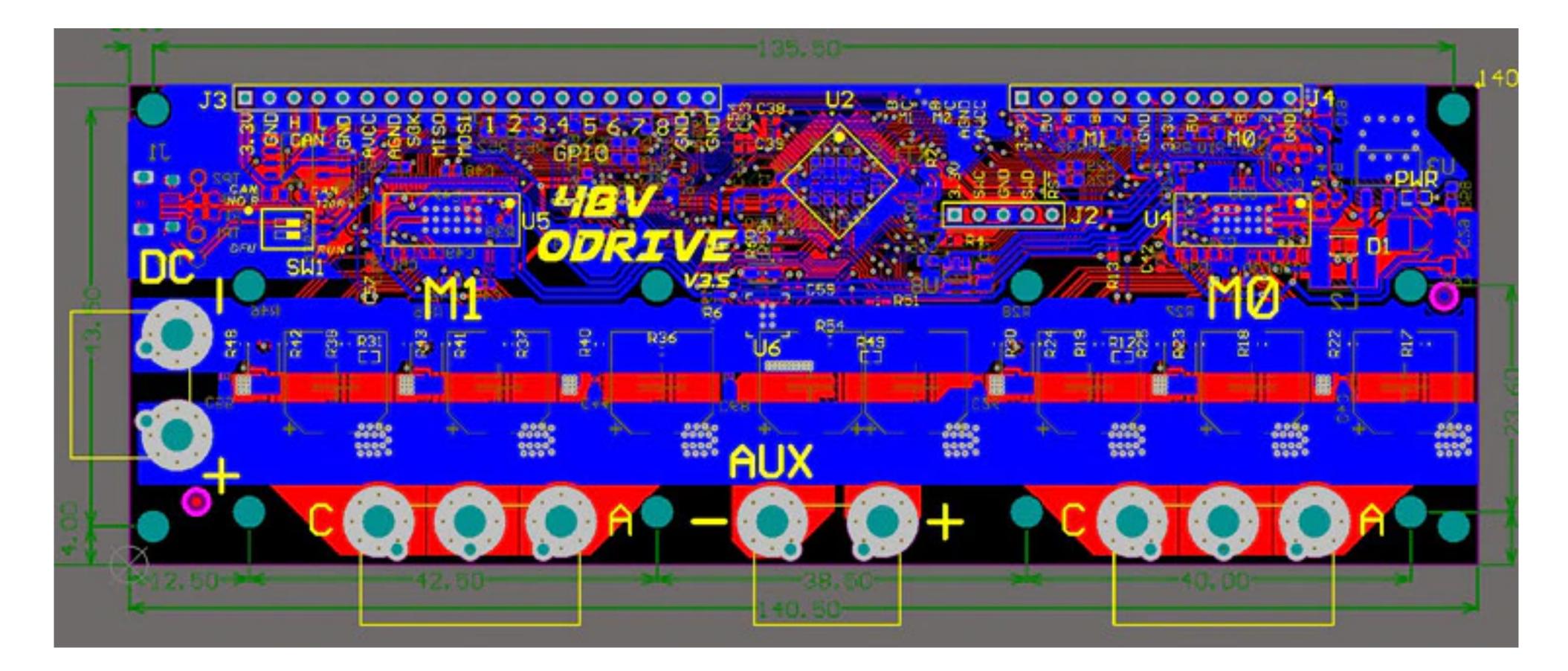

## **O-Drive MC** V3.1 Layout!

lecture 4 - Layout as an Art + Science | pcb.mit.edu | yaypcbs@mit.edu

## PCBDESIGN

## **O-Drive MC** V3.1 Layout!

lecture 4 - Layout as an Art + Science | pcb.mit.edu | yaypcbs@mit.edu

## DEBDESIGN

## **O-Drive MC** V3.1 Layout!